Product brief for 18-cell battery-cell controller IC

Rev. 3 — 25 January 2024

**Product brief**

### 1 General description

The MC33774A is a lithium-ion battery-cell controller IC designed for automotive applications, such as electric vehicles (EV) and hybrid electric vehicles (HEV). It can be used in industrial applications, such as energy storage systems (ESS) and uninterruptible power supply (UPS) systems.

The MC33774AxP1 (MC33774ATP1 for TPL isolated communication/MC33774ASP1 for SPI communication) is the premium version of the MC33774AxA1 (MC33774ATA1 for TPL isolated communication/MC33774ASA1 for SPI communication) for higher battery voltage and improved accuracy.

These devices support ISO 26262 ASIL D compliant high-precision cell voltage and temperature measurements, along with various cell-voltage balancing strategies. Aside from a SPI interface to enable direct communication with the host MCU, they alternatively provide a daisy-chain communication interface (TPL), which supports capacitive and inductive isolation between nodes.

### 2 Features and benefits

- AEC-Q100 grade 1 qualified: -40 °C to 125 °C ambient temperature range

- ISO 26262 ASIL D support for cell voltage and cell temperature measurements from the host microcontroller unit (MCU) to the cell

- Cell voltage measurement

- 4 to 18 cells per device

- Supports bus bars voltage measurement with -3 V to +5 V input voltage

- 16-bit resolution and up to ±0.8 mV typical measurement accuracy with ultra low long-term drift

- Integrated configurable digital filter

- External temperature and auxiliary voltage measurements

- One analog input for absolute measurement, 5 V input range

- Eight analog inputs configurable as absolute or ratiometric, 5 V input range

- 16-bit resolution and ±5 mV typical measurement accuracy

- Integrated configurable digital filter

- Internal measurement

- Two redundant internal temperature sensors

- Supply voltages

- External transistor current

- Cell voltage balancing

- 18 internal balancing field effect transistors (FET), up to 360 mA peak with 0.5 Ω R<sub>DSon</sub> per channel (typ.)

- Support for simultaneous passive balancing of all channels with automatic odd/even sequence

- Global balancing timeout timer

- Timer controlled balancing with individual timers with 10 s resolution and up to 45 h duration

- Voltage controlled balancing with global and individual undervoltage thresholds

- Temperature controlled balancing; if balancing resistors or the IC are in overtemperature, balancing is interrupted

- Configurable pulse width modulation (PWM) duty cycle balancing

- Automatic pause of balancing during measurement with configurable filter settling time

- Configurable delay of the start of balancing after transition to sleep

- Automatic discharge of the battery pack (emergency discharge)

- Constant current cell balancing to compensate the balancing current variation because of cell voltage variation

- I<sup>2</sup>C-bus master interface to control external devices, for example, EEPROMs and security ICs

- Configurable alarm output

- Cyclic wake-up to monitor the pack and the balancing function during sleep

- Capability to wake up the host MCU via daisy chain in case of a fault event

- Host interface supporting SPI or isolated daisy chain communication (TPL3)

- 2 Mbit/s data rate for TPL interface

- 4 Mbit/s data rate for SPI interface

- TPL3 daisy chain communication supports

- Two-wire daisy chain with capacitive or inductive isolation

- Protocol supporting up to six daisy chains and 62 nodes per chain

- Unique device ID with dynamic addressing

- Operation modes

- Active mode FP (12 mA typ.)

- Sleep mode LP (60 µA typ.)

- Deep Sleep mode ULP (15 μA typ.)

Product brief for 18-cell battery-cell controller IC

## **3** Applications

Automotive:

- (Plug-in) hybrid electric vehicle battery management system

- Electric vehicle battery management system

Industrial:

- Stationary ESS

- UPS systems

## 4 Ordering information

| Table 1. Ordering in | formation |                                                                                                                |           |  |  |

|----------------------|-----------|----------------------------------------------------------------------------------------------------------------|-----------|--|--|

| Type number          | Package   |                                                                                                                |           |  |  |

|                      | Name      | Description                                                                                                    | Version   |  |  |

| MC33774A             | LQFP64    | Plastic, thermal enhanced low profile quad flat package;<br>64 terminals; 0.50 mm pitch; 10 x 10 x 1.4 mm body | SOT1510-2 |  |  |

### 4.1 Ordering options

Table 2.

Part numbers

| Type number   | Description                      |

|---------------|----------------------------------|

| MC33774ATA1AE | Advanced version - TPL interface |

| MC33774ASA1AE | Advanced version - SPI interface |

| MC33774ATP1AE | Premium version - TPL interface  |

| MC33774ASP1AE | Premium version - SPI interface  |

4 / 25

Product brief for 18-cell battery-cell controller IC

### 5 Block diagram

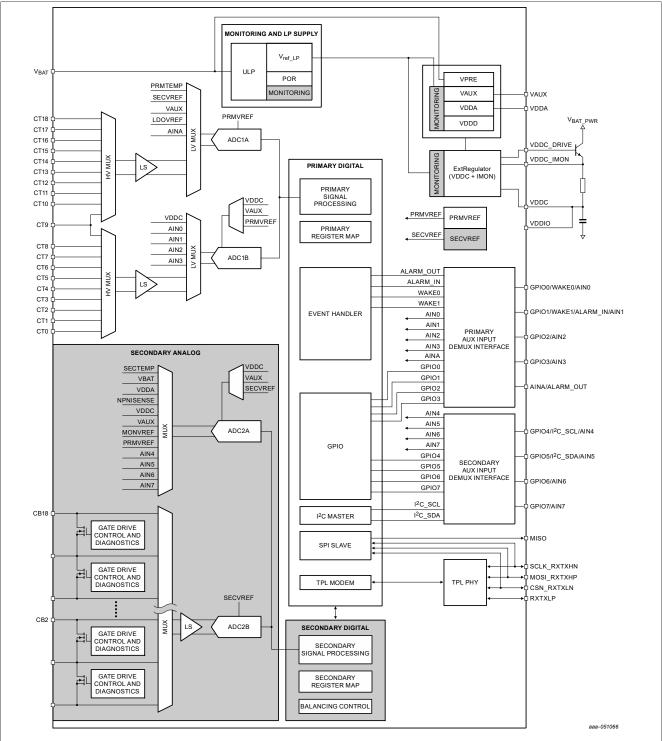

Figure 1 shows the general architecture of the MC33774A.

Figure 1. Simplified internal block diagram

Product brief for 18-cell battery-cell controller IC

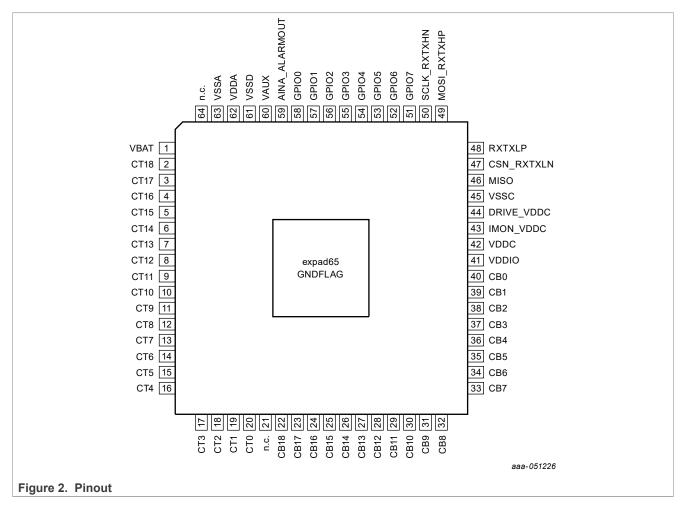

### 6 Pinning information

#### 6.1 Pinout diagram

#### 6.2 Pin description

#### Table 3. Pin description

| Symbol | Pin | Description                 |

|--------|-----|-----------------------------|

| VBAT   | 1   | Supply input of the product |

| CT18   | 2   | Cell terminal 18 input      |

| CT17   | 3   | Cell terminal 17 input      |

| CT16   | 4   | Cell terminal 16 input      |

| CT15   | 5   | Cell terminal 15 input      |

| CT14   | 6   | Cell terminal 14 input      |

| CT13   | 7   | Cell terminal 13 input      |

| CT12   | 8   | Cell terminal 12 input      |

| CT11   | 9   | Cell terminal 11 input      |

| CT10   | 10  | Cell terminal 10 input      |

PB\_MC33774A

© 2024 NXP B.V. All rights reserved.

Product brief for 18-cell battery-cell controller IC

| Table 3. Pin descri | ptioncontinued |                                                                                                                                         |

|---------------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| Symbol              | Pin            | Description                                                                                                                             |

| CT9                 | 11             | Cell terminal 9 input                                                                                                                   |

| CT8                 | 12             | Cell terminal 8 input                                                                                                                   |

| CT7                 | 13             | Cell terminal 7 input                                                                                                                   |

| CT6                 | 14             | Cell terminal 6 input                                                                                                                   |

| CT5                 | 15             | Cell terminal 5 input                                                                                                                   |

| CT4                 | 16             | Cell terminal 4 input                                                                                                                   |

| CT3                 | 17             | Cell terminal 3 input                                                                                                                   |

| CT2                 | 18             | Cell terminal 2 input                                                                                                                   |

| CT1                 | 19             | Cell terminal 1 input                                                                                                                   |

| CT0                 | 20             | Cell terminal 0 input                                                                                                                   |

| n.c.                | 21             | Not connected                                                                                                                           |

| CB18                | 22             | <ol> <li>Secondary cell terminal 18 input</li> <li>High input for cell 17 balancing</li> </ol>                                          |

| CB17                | 23             | <ol> <li>Secondary cell terminal 17 input</li> <li>Low input for cell 17 balancing</li> <li>High input for cell 16 balancing</li> </ol> |

| CB16                | 24             | <ol> <li>Secondary cell terminal 16 input</li> <li>Low input for cell 16 balancing</li> <li>High input for cell 15 balancing</li> </ol> |

| CB15                | 25             | <ol> <li>Secondary cell terminal 15 input</li> <li>Low input for cell 15 balancing</li> <li>High input for cell 14 balancing</li> </ol> |

| CB14                | 26             | <ol> <li>Secondary cell terminal 14 input</li> <li>Low input for cell 14 balancing</li> <li>High input for cell 13 balancing</li> </ol> |

| CB13                | 27             | <ol> <li>Secondary cell terminal 13 input</li> <li>Low input for cell 13 balancing</li> <li>High input for cell 12 balancing</li> </ol> |

| CB12                | 28             | <ol> <li>Secondary cell terminal 12 input</li> <li>Low input for cell 12 balancing</li> <li>High input for cell 11 balancing</li> </ol> |

| CB11                | 29             | <ol> <li>Secondary cell terminal 11 input</li> <li>Low input for cell 11 balancing</li> <li>High input for cell 10 balancing</li> </ol> |

| CB10                | 30             | <ol> <li>Secondary cell terminal 10 input</li> <li>Low input for cell 10 balancing</li> <li>High input for cell 9 balancing</li> </ol>  |

| CB9                 | 31             | <ol> <li>Secondary cell terminal 9 input</li> <li>Low input for cell 9 balancing</li> <li>High input for cell 8 balancing</li> </ol>    |

| CB8                 | 32             | <ol> <li>Secondary cell terminal 8 input</li> <li>Low input for cell 8 balancing</li> <li>High input for cell 7 balancing</li> </ol>    |

| CB7                 | 33             | <ol> <li>Secondary cell terminal 7 input</li> <li>Low input for cell 7 balancing</li> <li>High input for cell 6 balancing</li> </ol>    |

#### Table 3. Pin description...continued

PB\_MC33774A Product brief

| Table 3. | Pin | descriptioncontinued |

|----------|-----|----------------------|

|----------|-----|----------------------|

| Symbol      | Pin | Description                                                                                                                                                                                             |

|-------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CB6         | 34  | <ol> <li>Secondary cell terminal 6 input</li> <li>Low input for cell 6 balancing</li> <li>High input for cell 5 balancing</li> </ol>                                                                    |

| CB5         | 35  | <ol> <li>Secondary cell terminal 5 input</li> <li>Low input for cell 5 balancing</li> <li>High input for cell 4 balancing</li> </ol>                                                                    |

| CB4         | 36  | <ol> <li>Secondary cell terminal 4 input</li> <li>Low input for cell 4 balancing</li> <li>High input for cell 3 balancing</li> </ol>                                                                    |

| СВ3         | 37  | <ol> <li>Secondary cell terminal 3 input</li> <li>Low input for cell 3 balancing</li> <li>High input for cell 2 balancing</li> </ol>                                                                    |

| CB2         | 38  | <ol> <li>Secondary cell terminal 2 input</li> <li>Low input for cell 2 balancing</li> <li>High input for cell 1 balancing</li> </ol>                                                                    |

| CB1         | 39  | <ol> <li>Secondary cell terminal 1 input</li> <li>Low input for cell 1 balancing</li> <li>High input for cell 0 balancing</li> </ol>                                                                    |

| CB0         | 40  | <ol> <li>Secondary cell terminal 0 input</li> <li>Low input for cell 0 balancing</li> </ol>                                                                                                             |

| VDDIO       | 41  | External VDDIO supply input.                                                                                                                                                                            |

| VDDC        | 42  | External VDDC supply input.                                                                                                                                                                             |

| IMON_VDDC   | 43  | External NPN monitoring input.                                                                                                                                                                          |

| DRIVE_VDDC  | 44  | External NPN base output.                                                                                                                                                                               |

| VSSC        | 45  | VDDIO and VDDC ground reference.                                                                                                                                                                        |

| MISO        | 46  | SPI slave data output to master.                                                                                                                                                                        |

| CSN_RXTXLN  | 47  | <ol> <li>SPI chip select input from master</li> <li>TPLRX negative input from lower node</li> <li>TPLTX negative output to lower node</li> </ol>                                                        |

| RXTXLP      | 48  | <ol> <li>TPLRX positive input from lower node</li> <li>TPLTX positive output to lower node</li> </ol>                                                                                                   |

| MOSI_RXTXHP | 49  | <ol> <li>SPI slave data input from master</li> <li>TPLRX positive input from upper node</li> <li>TPLTX positive output to upper node</li> </ol>                                                         |

| SCLK_RXTXHN | 50  | <ol> <li>SPI clock input from master</li> <li>TPLRX negative input from upper node</li> <li>TPLTX negative output to upper node</li> </ol>                                                              |

| GPIO7       | 51  | <ol> <li>Analog input AIN7 for ratiometric measurement to VAUX/VDDC</li> <li>Analog input AIN7 for absolute measurement</li> <li>General-purpose input 7</li> <li>General-purpose output 7</li> </ol>   |

| GPIO6       | 52  | <ol> <li>Analog input AIN6 for ratiometric measurement to VAUX / VDDC</li> <li>Analog input AIN6 for absolute measurement</li> <li>General-purpose input 6</li> <li>General-purpose output 6</li> </ol> |

| Symbol        | Pin      | Description                                                                                                                                                                                                                                         |

|---------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GPIO5         | 53       | <ol> <li>Analog input AIN5 for ratiometric measurement to VAUX/VDDC</li> <li>Analog input AIN5 for absolute measurement</li> <li>General-purpose input 5</li> <li>General-purpose output 5</li> <li>I2CSDA</li> </ol>                               |

| GPIO4         | 54       | <ol> <li>Analog input AIN4 for ratiometric measurement to VAUX/VDDC</li> <li>Analog input AIN4 for absolute measurement</li> <li>General-purpose input 4</li> <li>General-purpose output 4</li> <li>I2CSCL</li> </ol>                               |

| GPIO3         | 55       | <ol> <li>Analog input AIN3 for ratiometric measurement to VAUX/VDDC</li> <li>Analog input AIN3 for absolute measurement</li> <li>General-purpose input 3</li> <li>General-purpose output 3</li> </ol>                                               |

| GPIO2         | 56       | <ol> <li>Analog input AIN2 for ratiometric measurement to VAUX/VDDC</li> <li>Analog input AIN2 for absolute measurement</li> <li>General-purpose input 2</li> <li>General-purpose output 2</li> </ol>                                               |

| GPIO1         | 57       | <ol> <li>Analog input AIN1 for ratiometric measurement to VAUX/VDDC</li> <li>Analog input AIN1 for absolute measurement</li> <li>General-purpose input 1</li> <li>General-purpose output 1</li> <li>Wake-up input 1</li> <li>Alarm input</li> </ol> |

| GPIO0         | 58       | <ol> <li>Analog input AIN0 for ratiometric measurement to VAUX/VDDC</li> <li>Analog input AIN0 for absolute measurement</li> <li>General-purpose input 0</li> <li>General-purpose output 0</li> <li>Wake-up input 0</li> </ol>                      |

| AINA_ALARMOUT | 59       | <ol> <li>Analog input AINA for absolute measurement</li> <li>Alarm output</li> </ol>                                                                                                                                                                |

| VAUX          | 60       | Supply output for external sensors.                                                                                                                                                                                                                 |

| VSSD          | 61       | Digital ground.                                                                                                                                                                                                                                     |

| VDDA          | 62       | Internal analog supply. Should be connected to a 100 nF capacitor. Should not be used for application.                                                                                                                                              |

| VSSA          | 63       | Analog ground.                                                                                                                                                                                                                                      |

| n.c.          | 64       | Not connected.                                                                                                                                                                                                                                      |

| GNDFLAG       | Expad 65 | Grounded exposed pad.                                                                                                                                                                                                                               |

## 7 Limiting values

#### 7.1 MC33774AxA1 limiting values

#### Table 4. Limiting values

In accordance with the Absolute Maximum Rating System (IEC 60134).

| Symbol           | Parameter    | Conditions | Min  | Тур | Max | Unit |

|------------------|--------------|------------|------|-----|-----|------|

| V <sub>BAT</sub> | VBAT voltage |            | -0.3 | -   | 84  | V    |

### 7.2 MC33774AxP1 limiting values

#### Table 5.Limiting values

In accordance with the Absolute Maximum Rating System (IEC 60134).

| Symbol           | Parameter    | Conditions | Min  | Тур | Max | Unit |

|------------------|--------------|------------|------|-----|-----|------|

| V <sub>BAT</sub> | VBAT voltage |            | -0.3 | -   | 94  | V    |

### 7.3 MC33774A common limiting values

#### Table 6. Common limiting values

In accordance with the Absolute Maximum Rating System (IEC 60134).

| Symbol                       | Parameter                                | Conditions                   | Min  | Тур | Max           | Unit |

|------------------------------|------------------------------------------|------------------------------|------|-----|---------------|------|

| V <sub>dif(CT)</sub>         | Cell terminal input differential voltage |                              | -5   | -   | 10            | V    |

| I <sub>i(CTn)</sub>          | cell terminal input current              | open load detection disabled | -500 | -   | 500           | nA   |

| V <sub>i(dif)bal</sub>       | balancing input differential voltage     |                              | -4.5 | -   | 12.5          | V    |

| I <sub>i(bal)</sub>          | input current on balancing pins          |                              | -    | -   | 330           | mA   |

| V <sub>DDC</sub>             | VDDC voltage                             |                              | -0.3 | -   | 5.5           | V    |

| V <sub>DDIO</sub>            | VDDIO voltage                            |                              | -0.3 | -   | 5.5           | V    |

| V <sub>AUX</sub>             | VAUX voltage                             |                              | -0.3 | -   | 4             | V    |

| V <sub>GPIOx</sub>           | GPIOx voltage                            |                              | -0.3 | -   | VDDC +<br>0.5 | V    |

| V <sub>AINA</sub>            | AINA and ALARM <sub>OUT</sub> voltage    |                              | -0.3 | -   | VDDC +<br>0.5 | V    |

| $V_{\text{bus}(\text{TPL})}$ | voltage on TPL communication bus pins    | Relative to VSSC             | -27  | -   | 40            | V    |

| Thermal maxir                | num ratings                              | 1                            |      |     |               |      |

| Tj                           | junction temperature                     |                              | -40  | -   | 165           | °C   |

| T <sub>stg</sub>             | storage temperature                      |                              | -55  | -   | 150           | °C   |

## 8 Electrical characteristics

### 8.1 MC33774AxA1 electrical characteristics

#### Table 7. Electrical characteristics

Vbat = 9 V to 81 V; Ta = -40 °C to 125 °C; Tj = -40 °C to 150 °C; all voltages are defined with respect to ground; positive currents flow into the IC. Typical values are given at Vbat = 72 V; Ta = 25 °C unless otherwise specified.

| Symbol                         | Parameter                                       | Conditions                                                           | Min  | Тур | Max | Unit |

|--------------------------------|-------------------------------------------------|----------------------------------------------------------------------|------|-----|-----|------|

| VBAT                           | L                                               |                                                                      |      |     |     |      |

| V <sub>BAT</sub>               | VBAT operating range                            |                                                                      | 9    | -   | 81  | V    |

| V <sub>BAT(th)ov</sub>         | VBAT overvoltage threshold                      |                                                                      | 81   | -   | 83  | V    |

| Cell voltage meas              | surement accuracy for primary mea               | surement - begin of life                                             |      |     | •   | -    |

| V <sub>err(meas)</sub> (LPF1)  | Measurement error voltage (LFP1)                | VC <sub>x</sub> = 0 V to 3.7 V; T <sub>j</sub> = -40 °C<br>to 105 °C | -1   | -   | 1   | mV   |

| V <sub>err(meas)(NMC1)</sub>   | Measurement error voltage (NMC1)                | $VC_x = 0 V \text{ to } 4.5 V; T_j = -40 °C \text{ to } 105 °C$      | -1.3 | -   | 1.3 | mV   |

| Cell voltage meas              | surement accuracy for primary mea               | surement - end of life                                               |      | I   |     |      |

| V <sub>err(meas)(LFP3)</sub>   | Measurement error voltage (LFP3)                | $VC_x = 0 V \text{ to } 3.7 V; T_j = -40 °C \text{ to } 125 °C$      | -1.5 | -   | 1.5 | mV   |

| V <sub>err(meas)(NMC3)</sub>   | Measurement error voltage (NMC3)                | $VC_x = 0 V \text{ to } 4.5 V; T_j = -40 °C \text{ to } 125 °C$      | -2.0 | -   | 2.0 | mV   |

| TPL current                    |                                                 |                                                                      | I    |     |     |      |

| I <sub>VDDC(TPL)wait</sub>     | TPL current on VDDC, device in waiting state    | 2 RX ON,No TX                                                        | -    | -   | 1.4 | mA   |

| I <sub>VDDC</sub> (TPL)forward | TPL current on VDDC, device in forward state    | 1 RX ON,1 TX ON(TX averaged<br>on bit period)                        | -    | -   | 9.2 | mA   |

| IVDDC(TPL)respond              | TPL current on VDDC, device in responding state | NO RX, 2 TX ON(TX averaged on bit period)                            | -    | -   | 17  | mA   |

### 8.2 MC33774AxP1 electrical characteristics

#### Table 8. Electrical characteristics

Vbat = 9 V to 90 V; Ta = -40 °C to 125 °C; Tj = -40 °C to 150 °C; all voltages are defined with respect to ground; positive currents flow into the IC. Typical values are given at Vbat = 72 V; Ta = 25 °C unless otherwise specified.

| Symbol                         | Parameter                                                   | Conditions                                               | Min  | Тур | Max | Unit |

|--------------------------------|-------------------------------------------------------------|----------------------------------------------------------|------|-----|-----|------|

| VBAT                           |                                                             |                                                          | I    |     | I   |      |

| V <sub>BAT</sub>               | VBAT operating range                                        |                                                          | 9    | -   | 90  | V    |

| V <sub>BAT(th)ov</sub>         | VBAT overvoltage threshold                                  |                                                          | 90   | -   | 93  | V    |

| Cell voltage meas              | urement accuracy for primary mea                            | surement - begin of life                                 |      |     | ·   | -    |

| V <sub>err(meas)(A)(CTx)</sub> | Cell voltage measurement error<br>CTx, range A. (LFP)       | Vcell = 0 V3.7 V, Tj = -40 °C<br>115 °C, VBAT = 9 V 81 V | -0.8 | -   | 0.8 | mV   |

| V <sub>err(meas)(B)(CTx)</sub> | Cell voltage measurement error<br>CTx, range B. (NMC)       | Vcell = 0 V4.5 V, Tj = -40 °C<br>115 °C, VBAT = 9 V 81 V | -1   | -   | 1   | mV   |

| Cell voltage meas              | urement accuracy for primary mea                            | surement - end of life                                   |      |     |     |      |

| V <sub>err(meas)(E)(CTx)</sub> | Cell voltage measurement error<br>CTx, range E. (LFP cells) | Vcell = 0 V3.7 V, Tj = -40 °C<br>115 °C, VBAT = 9 V 81 V | -1.2 | -   | 1.2 | mV   |

| V <sub>err(meas)(F)(CTx)</sub> | Cell voltage measurement error<br>CTx, range F. (NMC cells) | Vcell = 0 V4.5 V, Tj = -40 °C<br>115 °C, VBAT = 9 V 81 V | -1.5 | -   | 1.5 | mV   |

© 2024 NXP B.V. All rights reserved.

### Product brief for 18-cell battery-cell controller IC

#### Table 8. Electrical characteristics...continued

Vbat = 9 V to 90 V; Ta = -40 °C to 125 °C; Tj = -40 °C to 150 °C; all voltages are defined with respect to ground; positive currents flow into the IC. Typical values are given at Vbat = 72 V; Ta = 25 °C unless otherwise specified.

| Symbol                     | Parameter                                       | Conditions                                    | Min | Тур | Мах  | Unit |  |  |

|----------------------------|-------------------------------------------------|-----------------------------------------------|-----|-----|------|------|--|--|

| TPL current                |                                                 |                                               |     |     |      |      |  |  |

| I <sub>VDDC(TPL)wait</sub> | TPL current on VDDC, device in waiting state    | 2 RX ON,No TX                                 | -   | -   | 1.4  | mA   |  |  |

| IVDDC(TPL)forward          | TPL current on VDDC, device in forward state    | 1 RX ON,1 TX ON(TX averaged<br>on bit period) | -   | -   | 11.2 | mA   |  |  |

| IVDDC(TPL)respond          | TPL current on VDDC, device in responding state | NO RX, 2 TX ON(TX averaged<br>on bit period)  | -   | -   | 21   | mA   |  |  |

### 8.3 MC33774A common electrical characteristics

#### Table 9. Characteristics

Vbat = 9 V to 81 V (MC33774AxA1) / 90V (MC33774AxP1); Ta = -40 °C to 125 °C; Tj = -40 °C to 150 °C; all voltages are defined with respect to ground; positive currents flow into the IC. Typical values are given at Vbat = 72 V; Ta = 25 °C unless otherwise specified.

| Symbol                           | Parameter                                                                                                           | Conditions                                                                                                                                                                       | Min  | Тур | Мах  | Unit |

|----------------------------------|---------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|------|------|

| VBAT                             |                                                                                                                     |                                                                                                                                                                                  | ·    |     |      | -    |

| V <sub>BAT(th)uv</sub>           | VBAT undervoltage threshold                                                                                         |                                                                                                                                                                                  | 7    | 8   | 9    | V    |

| V <sub>BAT(th)lv</sub>           | VBAT low-voltage (LV) threshold                                                                                     | FP and FPC modes and LP mode with cell balancing                                                                                                                                 | 10.5 | 12  | 13.5 | V    |

| $\Delta V_{max1(VBAT-upperCT)}$  | Maximum voltage difference 1<br>between battery supply voltage<br>and pin CT18 or highest CTn                       | V <sub>bat</sub> = 35 V to maximum supply voltage                                                                                                                                | -2.1 | -   | 2.5  | V    |

| ∆V <sub>max2(VBAT-upperCT)</sub> | Maximum voltage difference<br>between battery supply voltage<br>and pin CT18 or highest CTn                         | V <sub>bat</sub> = 9 V +1.5 V to 35 V                                                                                                                                            | -1.5 | -   | 2    | V    |

| $\Delta V_{bal(VBAT-upperCB)}$   | Maximum voltage difference<br>between battery supply voltage<br>and pin CB18 or highest CBn                         | $T_{j} = -40 \text{ °C to } 150 \text{ °C}, V_{bat} = 9 \text{ V}$<br>to 81V, $V_{cell} = -5 \text{ V}$ to 5 V                                                                   | -0.4 | -   | 0.4  | V    |

| Current consumptio               | on la                                                                           |                                                                                                                                                                                  |      | 1   |      |      |

| BAT(ULP)                         | IBAT current in Deep Sleep mode                                                                                     | Tj= -40 °C85 °C                                                                                                                                                                  | -    | -   | 19   | μA   |

| BAT(LP)                          | IBAT current in Sleep mode                                                                                          | Tj= -40 °C125 °C                                                                                                                                                                 | -    | -   | 115  | μA   |

| BAT(add)LP                       | Additional IBAT current in Sleep<br>mode in sleep mode due to<br>balancing                                          | sleep mode with balancing<br>enabled                                                                                                                                             | -    | -   | 2.9  | mA   |

| BAT(FP)                          | Full Power mode current<br>consumption measuring all cell<br>voltages and auxiliary inputs.                         | No external load. No cell<br>balancing.                                                                                                                                          | -    | -   | 14.9 | mA   |

| IBAT(FPC)2                       | Cyclic mode current consumption<br>measuring all cell voltages,<br>primary auxiliary inputs, and<br>module voltage. | No secondary measurement. No<br>balancing. No external current<br>consumption. No communication.                                                                                 | -    | -   | 12.3 | mA   |

| BATCB(FPC)                       | IBAT additional current in FP or FPC mode when all CB enable                                                        | All cell balancing enabled.                                                                                                                                                      | -    | -   | 700  | uA   |

| ΔI <sub>BAT(FP)</sub>            | IC to IC operating current<br>imbalance                                                                             | Ta = -40 °C to 125 °C, Vbat = 45<br>V, Ta and Vbat are the same for<br>both ICs, Active mode/all ADCs<br>running/No balancing operation/<br>No communication/No external<br>load | -    | -   | 400  | μA   |

### Product brief for 18-cell battery-cell controller IC

#### Table 9. Characteristics...continued

Vbat = 9 V to 81 V (MC33774AxA1) / 90V (MC33774AxP1); Ta = -40 °C to 125 °C; Tj = -40 °C to 150 °C; all voltages are defined with respect to ground; positive currents flow into the IC. Typical values are given at Vbat = 72 V; Ta = 25 °C unless otherwise specified.

| Symbol                       | Parameter                                             | Conditions                                                                                                             | Min   | Тур   | Max   | Unit   |

|------------------------------|-------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|--------|

| VAUX                         |                                                       |                                                                                                                        |       |       |       |        |

| V <sub>AUX</sub>             | VAUX output voltage                                   |                                                                                                                        | 3.19  | 3.3   | 3.41  | V      |

| I <sub>VAUX</sub>            | VAUX external current capability                      |                                                                                                                        | -     | -     | 5     | mA     |

| VDDC                         |                                                       |                                                                                                                        | I     | I     |       |        |

| V <sub>DDC</sub>             | VDDC output voltage                                   |                                                                                                                        | 4.85  | 5.0   | 5.15  | V      |

| I <sub>VDDC</sub>            | External VDDC current drive capability                | Ta = -40 °C to 125 °C                                                                                                  | -     | -     | 15    | mA     |

| Internal temperat            | ure measurement                                       | 1                                                                                                                      | I     | I     |       |        |

| T <sub>j(meas)</sub>         | IC temperature measurement range                      |                                                                                                                        | -45   | -     | 155   | °C     |

| $\Delta T_{j(meas)}$         | IC temperature measurement error                      | Range to be measured is -40 °C to 150 °C                                                                               | -3    | -     | 3     | °C     |

| Overtemperature p            | protection                                            | I                                                                                                                      | I     |       | 1     |        |

| T <sub>sd(th)</sub>          | Shutdown temperature threshold                        | Of VPRE regulator                                                                                                      | 160   | -     | 175   | °C     |

| Measurement res              | olution                                               | 1                                                                                                                      | I     |       | 1     |        |

| V <sub>meas(res)VBAT</sub>   | Measured voltage resolution                           |                                                                                                                        | -     | 3.128 | -     | mV/LSB |

| V <sub>meas(res)</sub>       | Measured voltage resolution                           |                                                                                                                        | -     | 154   | -     | µV/LSB |

| T <sub>meas(res)</sub>       | Primary and secondary measured temperature resolution |                                                                                                                        | -     | 32.4  | -     | mK/LSB |

| Vmeas(res)(supply)           | Supply voltage measurement resolution (VAUX, VDDC)    |                                                                                                                        | -     | 308   | -     | uV/LSB |

| V <sub>meas(res)(vdda)</sub> | Supply voltage measurement resolution (VDDA)          |                                                                                                                        | -     | 154   | -     | uV/LSB |

| Measurement acc              | quisition                                             |                                                                                                                        | I     |       |       |        |

| N <sub>s(PI)</sub>           | Number of periodic integrator samples                 |                                                                                                                        | 16    | -     | 511   |        |

| N <sub>s(AI)</sub>           | Number of application integrator samples              |                                                                                                                        | 16    | -     | 65534 |        |

| VBAT measureme               | ent accuracy                                          | I                                                                                                                      | I     |       |       |        |

| V <sub>I(acc)VBAT</sub>      | Measured voltage minimum accuracy                     | Tj = -40 °C to 115 °C, VBAT ≥ 17<br>V at pin VBAT (wo Rvbat)                                                           | -50   | -     | 50    | mV     |

| $\Delta V_{I(meas)VBAT}$     | Measured Voltage Max Relative<br>Error                | Tj = -40 °C to 115 °C, VBAT ≥ 17<br>V at pin VBAT (wo Rvbat)                                                           | -     | -     | 0.3   | %      |

| Balancing                    |                                                       |                                                                                                                        | 1     |       | 1     |        |

| I <sub>bal2</sub>            | Balancing current                                     | T <sub>j</sub> = -40 °C to 125 °C, R <sub>bal</sub> =<br>10 to 450 Ω, no external load<br>current, 50 % duty cycle max | 0     | -     | 360   | mA     |

| I <sub>lim(bal)2</sub>       | Balancing current limit                               | Tj = -40 °C to 125 °C                                                                                                  | 360   | -     | 800   | mA     |

| R <sub>sw(bal)</sub>         | Balancing switch resistance                           | T <sub>j</sub> = -40 °C to 150 °C, V <sub>bat</sub> = 9 V<br>to 81 V, 4 to 18 cells                                    | -     | -     | 1.1   | Ω      |

| Analog inputs                | 1                                                     | 1                                                                                                                      | I     |       |       |        |

| V <sub>meas(aux)(abs)</sub>  | Auxiliary input measured voltage (absolute value)     |                                                                                                                        | 0     | -     | 5     | V      |

| E <sub>G(abs)1</sub>         | Absolute gain error 1                                 | T <sub>i</sub> = -40 °C to 115 °C                                                                                      | -0.08 | -     | 0.08  | %      |

PB\_MC33774A

© 2024 NXP B.V. All rights reserved.

### Product brief for 18-cell battery-cell controller IC

#### Table 9. Characteristics...continued

Vbat = 9 V to 81 V (MC33774AxA1) / 90V (MC33774AxP1); Ta = -40 °C to 125 °C; Tj = -40 °C to 150 °C; all voltages are defined with respect to ground; positive currents flow into the IC. Typical values are given at Vbat = 72 V; Ta = 25 °C unless otherwise specified.

| Symbol                         | Parameter                                    | Conditions                                                                                                  | Min                                       | Тур                           | Max                                      | Unit    |

|--------------------------------|----------------------------------------------|-------------------------------------------------------------------------------------------------------------|-------------------------------------------|-------------------------------|------------------------------------------|---------|

| E <sub>G(abs)2</sub>           | Absolute gain error 2                        | T <sub>j</sub> = -40 °C to 150 °C                                                                           | -0.12                                     | -                             | 0.12                                     | %       |

| V <sub>err(offset)(abs)</sub>  | Absolute offset error voltage                | T <sub>j</sub> = -40 °C to 150 °C                                                                           | -3                                        | -                             | 3                                        | mV      |

| E <sub>T(meas)</sub> ratiom1   | Ratiometric measurement total<br>error 1     | T <sub>j</sub> = -40 °C to 115 °C                                                                           | -0.006 -<br>0.15 %<br>* V <sub>AINx</sub> | -                             | 0.006 +<br>0.15 %<br>* V <sub>AINx</sub> | V       |

| E <sub>T(meas)</sub> ratiom2   | Ratiometric measurement total error 2        | T <sub>j</sub> = -40 °C to 150 °C                                                                           | -0.006 -<br>0.25 %<br>* V <sub>AINx</sub> | -                             | 0.006 +<br>0.25 %<br>* V <sub>AINx</sub> | V       |

| V <sub>meas(res)(abs)</sub>    | Measured voltage resolution                  | Absolute measurement (absolute reference voltage)                                                           | -                                         | 154                           | -                                        | µV/LSB  |

| V <sub>meas(res)(ratiom)</sub> | Measured voltage resolution                  | Ratiometric measurement (VAUX or VDDC)                                                                      | -                                         | 3.05176<br>x 10 <sup>-3</sup> | -                                        | % / LSB |

| GPIO                           | -                                            |                                                                                                             |                                           |                               |                                          |         |

| V <sub>OH(GPIO)</sub>          | Output logic high voltage on GPIO pins       | $I_{GPIO} = 1 \text{ mA Including routing}$<br>and all GPIOs / $I^2C$ driving at the<br>same time.          | V <sub>VDDC</sub> -<br>0.4V               | -                             | V <sub>VDDC</sub>                        | -       |

| V <sub>OL(GPIO)</sub>          | Output logic low voltage on GPIO pins        | I <sub>GPIO</sub> = 1 mA Including routing<br>and all GPIOs / I <sup>2</sup> C driving at the<br>same time. | -                                         | -                             | 0.4                                      | V       |

| I <sub>OH(tot)</sub> GPIO      | Total high-level output current on GPIO pins |                                                                                                             | -                                         | -                             | 8                                        | mA      |

| I <sub>OL(tot)</sub> GPIO      | Total low-level output current on GPIO pins  |                                                                                                             | -                                         | -                             | 20                                       | mA      |

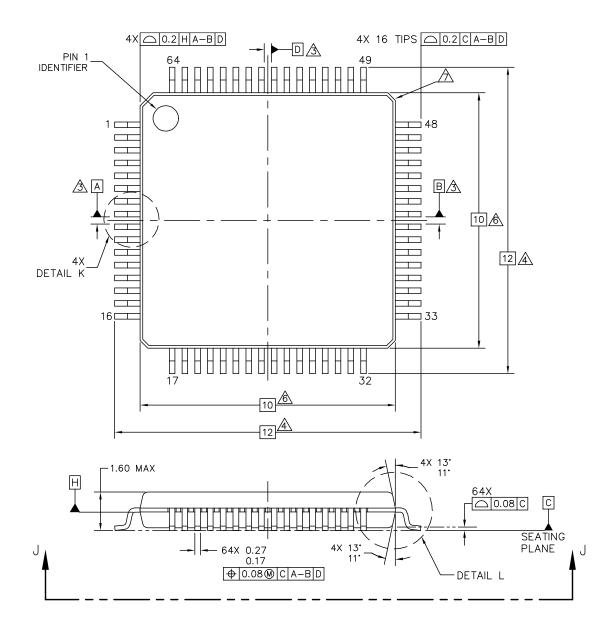

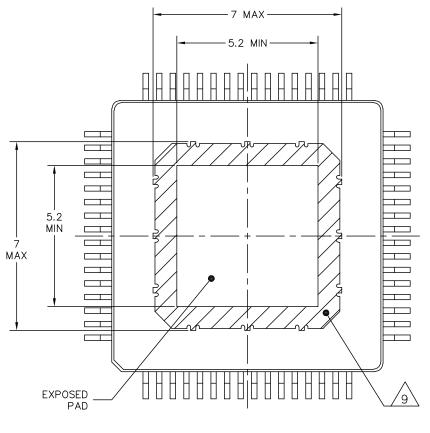

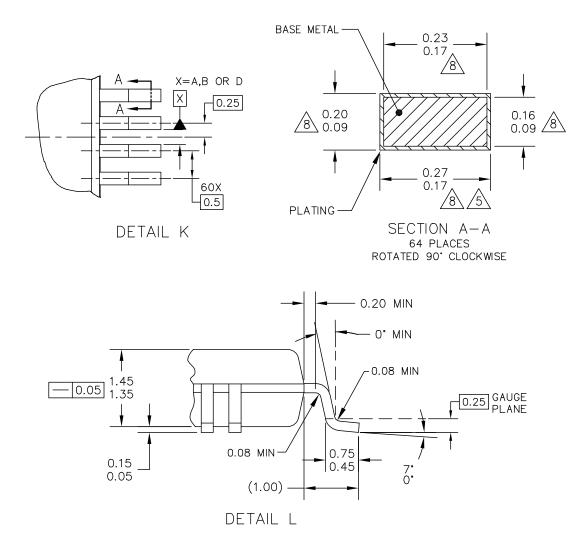

### 9 Package information

Package dimensions are provided in package drawings. To find the most current package outline drawing, go to <u>www.nxp.com</u> and perform a keyword search for the drawing's document number.

#### Table 10. Package outline

| Package        | Suffix | Package outline drawing number |

|----------------|--------|--------------------------------|

| 64-pin LQFP-EP | AE     | 98ASA10763D                    |

| © NXP SEMICONDUCTORS N. V.<br>ALL RIGHTS RESERVED | MECHANICAL OU | TLINE   | PRINT VERSION NOT    | TO SCALE   |

|---------------------------------------------------|---------------|---------|----------------------|------------|

| TITLE: LQFP, 10 X 10 X                            | 1.4 PKG,      | DOCUMEN | NT NO: 98ASA10763D   | REV: E     |

| 0.5 PITCH, 64LD,<br>6.1 x 6.1 EXPOSED PAD         |               | STANDAF | RD: JEDEC MS-026 BCC | )          |

|                                                   |               | S0T1510 | )-2 2                | 9 JUN 2018 |

VIEW J-J

| © NXP SEMICONDUCTORS N. V.<br>ALL RIGHTS RESERVED | MECHANICAL OU | TLINE   | PRINT VERSION N    | OT TO SCALE |

|---------------------------------------------------|---------------|---------|--------------------|-------------|

| TITLE: LQFP, 10 X 10 X                            | 1.4 PKG,      | DOCUMEN | NT NO: 98ASA10763D | REV: E      |

| 0.5 PITCH, 64LD,<br>6.1 x 6.1 EXPOSED PAD         |               | STANDAF | RD: JEDEC MS-026 B | CD          |

|                                                   |               | SOT1510 | )–2                | 29 JUN 2018 |

| © NXP SEMICONDUCTORS N. V.<br>ALL RIGHTS RESERVED | MECHANICAL OU | TLINE   | PRINT VERSION NO    | DT TO SCALE |

|---------------------------------------------------|---------------|---------|---------------------|-------------|

| 0.5 PITCH, 64LD,<br>6.1 x 6.1 EXPOSED PAD         |               | DOCUMEN | NT NO: 98ASA10763D  | REV: E      |

|                                                   |               | STANDAF | RD: JEDEC MS-026 BC | CD          |

|                                                   |               | S0T1510 | 0–2                 | 29 JUN 2018 |

#### Product brief for 18-cell battery-cell controller IC

NOTES:

- 1. DIMENSIONS ARE IN MILLIMETERS.

- 2. INTERPRET DIMENSIONS AND TOLERANCES PER ASME Y14.5M-1994.

- $\overline{3}$  datums a, b and d to be determined at datum plane H.

- 4 dimensions to be determined at seating plane C.

- DIMENSION DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL NOT CAUSE THE LEAD WIDTH TO EXCEED THE MAXIMUM DIMENSION BY MORE THAN 0.08 MM. DAMBAR CANNOT BE LOCATED ON THE LOWER RADIUS OR THE FOOT. MINIMUM SPACE BETWEEN PROTRUSION AND ADJACENT LEAD OR PROTRUSION 0.07 MM.

- DIMENSIONS DO NOT INCLUDE MOLD PROTRUSION. ALLOWABLE PROTRUSION IS 0.25 MM PER SIDE. DIMENSIONS ARE MAXIMUM PLASTIC BODY SIZE DIMENSIONS INCLUDING MOLD MISMATCH.

- $\triangle$  exact shape of each corner is optional.

- THESE DIMENSIONS APPLY TO THE FLAT SECTION OF THE LEAD BETWEEN 0.10 MM AND 0.25 MM FROM THE LEAD TIP.

- A HATCHED AREA REPRESENTS POSSIBLE MOLD FLASH ON EXPOSED PAD.

- A KEEP OUT ZONE REPRESENTS AREA ON PCB THAT MUST NOT HAVE ANY EXPOSED METAL (EG. TRACE/VIA) FOR PCB ROUTING DUE TO THE POSSIBILITY OF SHORTING TO TIE BAR/EXPOSED PAD.

| © NXP SEMICONDUCTORS N. V.<br>ALL RIGHTS RESERVED | MECHANICAL OU | TLINE   | PRINT VERSION NOT    | TO SCALE   |

|---------------------------------------------------|---------------|---------|----------------------|------------|

| 0.5 PITCH, 64LD,<br>$6.1 \times 6.1$ EXPOSED PAD  |               | DOCUMEN | NT NO: 98ASA10763D   | REV: E     |

|                                                   |               | STANDAF | RD: JEDEC MS-026 BCD |            |

|                                                   |               | S0T1510 | )-2 2                | 9 JUN 2018 |

## 10 Revision history

| Revision | Date             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|----------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| v.3      | 25 January 2024  | Updated <u>Figure 1</u> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| v.2      | 11 December 2023 | <ul> <li>Added MC33774AxP product description and characteristics in addition to the MC33774AxA single product initially described in the MC33774A v.1 product brief. As a consequence, the following changes have been done:</li> <li><u>General description</u>: Updated text</li> <li><u>Features and benefits</u>:<br/>Changed bullet item to " up to 360 mA peak with 0.5 Ω R<sub>DSon</sub> per channel (typ.)" from " up to 150 mA average with 0.5 Ω R<sub>DSon</sub> per channel (typ.)"</li> <li><u>Ordering information</u>: Updated <u>Oredering information</u> and <u>Ordering options</u></li> <li><u>Section 7</u>: Reorganized with MC33774AxA1 limiting values table, MC33774 AxP1 limiting values table, MC33774AxA1 limiting values table</li> <li><u>Electrical characteristics</u>: Reorganized with MC33774AxA1 limiting values table</li> <li><u>Package information</u>: Updated figures to most recent versions</li> <li><u>Revision history</u>: Updated to align with NXP style</li> </ul> |

| v.1      | 03 March 2023    | Initial version                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

#### Product brief for 18-cell battery-cell controller IC

### Legal information

#### Definitions

**Draft** — A draft status on a document indicates that the content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included in a draft version of a document and shall have no liability for the consequences of use of such information.

### Disclaimers

Limited warranty and liability — Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information. NXP Semiconductors takes no responsibility for the content in this document if provided by an information source outside of NXP Semiconductors.

In no event shall NXP Semiconductors be liable for any indirect, incidental, punitive, special or consequential damages (including - without limitation lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory.

Notwithstanding any damages that customer might incur for any reason whatsoever, NXP Semiconductors' aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the Terms and conditions of commercial sale of NXP Semiconductors.

**Right to make changes** — NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

**Applications** — Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

Customers are responsible for the design and operation of their applications and products using NXP Semiconductors products, and NXP Semiconductors accepts no liability for any assistance with applications or customer product design. It is customer's sole responsibility to determine whether the NXP Semiconductors product is suitable and fit for the customer's applications and products planned, as well as for the planned application and use of customer's third party customer(s). Customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products.

NXP Semiconductors does not accept any liability related to any default, damage, costs or problem which is based on any weakness or default in the customer's applications or products, or the application or use by customer's third party customer(s). Customer is responsible for doing all necessary testing for the customer's applications and products using NXP Semiconductors products in order to avoid a default of the applications and the products or of the application or use by customer's third party customer(s). NXP does not accept any liability in this respect.

Limiting values — Stress above one or more limiting values (as defined in the Absolute Maximum Ratings System of IEC 60134) will cause permanent damage to the device. Limiting values are stress ratings only and (proper) operation of the device at these or any other conditions above those given in the Recommended operating conditions section (if present) or the Characteristics sections of this document is not warranted. Constant or repeated exposure to limiting values will permanently and irreversibly affect the quality and reliability of the device.

Terms and conditions of commercial sale — NXP Semiconductors products are sold subject to the general terms and conditions of commercial sale, as published at https://www.nxp.com/profile/terms, unless otherwise agreed in a valid written individual agreement. In case an individual agreement is concluded only the terms and conditions of the respective agreement shall apply. NXP Semiconductors hereby expressly objects to applying the customer's general terms and conditions with regard to the purchase of NXP Semiconductors products by customer.

**No offer to sell or license** — Nothing in this document may be interpreted or construed as an offer to sell products that is open for acceptance or the grant, conveyance or implication of any license under any copyrights, patents or other industrial or intellectual property rights.

Suitability for use in automotive applications — This NXP product has been qualified for use in automotive applications. If this product is used by customer in the development of, or for incorporation into, products or services (a) used in safety critical applications or (b) in which failure could lead to death, personal injury, or severe physical or environmental damage (such products and services hereinafter referred to as "Critical Applications"), then customer makes the ultimate design decisions regarding its products and is solely responsible for compliance with all legal, regulatory, safety, and security related requirements concerning its products, regardless of any information or support that may be provided by NXP. As such, customer assumes all risk related to use of any products in Critical Applications and NXP and its suppliers shall not be liable for any such use by customer. Accordingly, customer will indemnify and hold NXP harmless from any claims, liabilities, damages and associated costs and expenses (including attorneys' fees) that NXP may incur related to customer's incorporation of any product in a Critical Application.

**Quick reference data** — The Quick reference data is an extract of the product data given in the Limiting values and Characteristics sections of this document, and as such is not complete, exhaustive or legally binding.

**Export control** — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from competent authorities.

**Translations** — A non-English (translated) version of a document, including the legal information in that document, is for reference only. The English version shall prevail in case of any discrepancy between the translated and English versions.

Security — Customer understands that all NXP products may be subject to unidentified vulnerabilities or may support established security standards or specifications with known limitations. Customer is responsible for the design and operation of its applications and products throughout their lifecycles to reduce the effect of these vulnerabilities on customer's applications and products. Customer's responsibility also extends to other open and/or proprietary technologies supported by NXP products for use in customer's applications. NXP accepts no liability for any vulnerability. Customer should regularly check security updates from NXP and follow up appropriately. Customer shall select products with security features that best meet rules, regulations, and standards of the intended application and make the ultimate design decisions regarding its products and is solely responsible for compliance with all legal, regulatory, and security related requirements concerning its products, regardless of any information or support that may be provided by NXP.

NXP has a Product Security Incident Response Team (PSIRT) (reachable at <u>PSIRT@nxp.com</u>) that manages the investigation, reporting, and solution release to security vulnerabilities of NXP products.

**NXP B.V.** — NXP B.V. is not an operating company and it does not distribute or sell products.

### Trademarks

Notice: All referenced brands, product names, service names, and trademarks are the property of their respective owners.

Product brief for 18-cell battery-cell controller IC

NXP — wordmark and logo are trademarks of NXP B.V.

Product brief for 18-cell battery-cell controller IC

### **Tables**

| Tab. 1. | Ordering information4 | Tab. 6.  | Common limiting values     | 10 |

|---------|-----------------------|----------|----------------------------|----|

| Tab. 2. | Part numbers4         | Tab. 7.  | Electrical characteristics | 11 |

| Tab. 3. | Pin description6      | Tab. 8.  | Electrical characteristics | 11 |

| Tab. 4. | Limiting values10     | Tab. 9.  | Characteristics            | 12 |

| Tab. 5. | Limiting values 10    | Tab. 10. | Package outline            | 15 |

|         |                       |          |                            |    |

Product brief for 18-cell battery-cell controller IC

## **Figures**

| Fig. 1. | Simplified internal block diagram5 | Fig. 2. | Pinout6 |

|---------|------------------------------------|---------|---------|

|         |                                    |         |         |

Product brief for 18-cell battery-cell controller IC

### Contents

| 1   | General description                    | 1  |

|-----|----------------------------------------|----|

| 2   | Features and benefits                  | 2  |

| 3   | Applications                           | 3  |

| 4   | Ordering information                   | 4  |

| 4.1 | Ordering options                       | 4  |

| 5   | Block diagram                          |    |

| 6   | Pinning information                    |    |

| 6.1 | Pinout diagram                         |    |

| 6.2 | Pin description                        |    |

| 7   | Limiting values                        |    |

| 7.1 | MC33774AxA1 limiting values            | 10 |

| 7.2 | MC33774AxP1 limiting values            |    |

| 7.3 | MC33774A common limiting values        |    |

| 8   | Electrical characteristics             |    |

| 8.1 | MC33774AxA1 electrical characteristics | 11 |

| 8.2 | MC33774AxP1 electrical characteristics | 11 |

| 8.3 | MC33774A common electrical             |    |

|     | characteristics                        | 12 |

| 9   | Package information                    | 15 |

| 10  | Revision history                       |    |

|     | Legal information                      |    |

Please be aware that important notices concerning this document and the product(s) described herein, have been included in section 'Legal information'.

© 2024 NXP B.V.

All rights reserved.

For more information, please visit: https://www.nxp.com

Date of release: 25 January 2024 Document identifier: PB\_MC33774A