# **PM823**

# Dual Synchronous 1.5A/1.5A Step-down Buck Regulators with 525 mA LDO

Rev. 5 — 27 February 2024

Product data sheet

#### **Product overview**

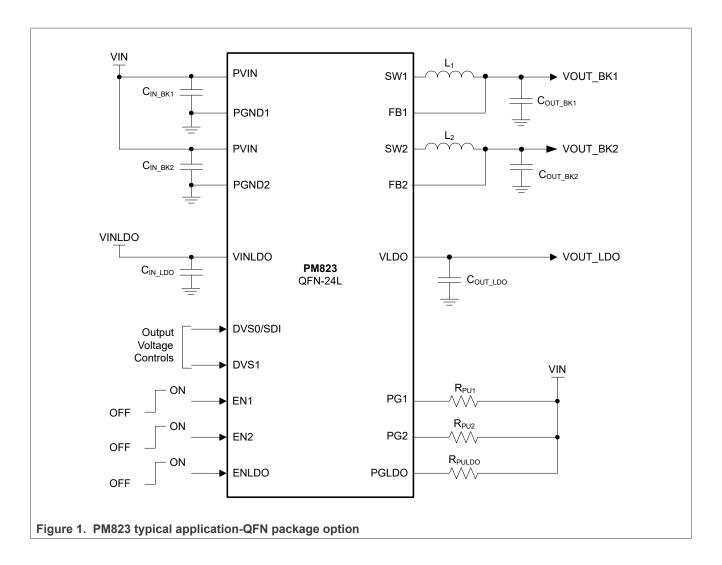

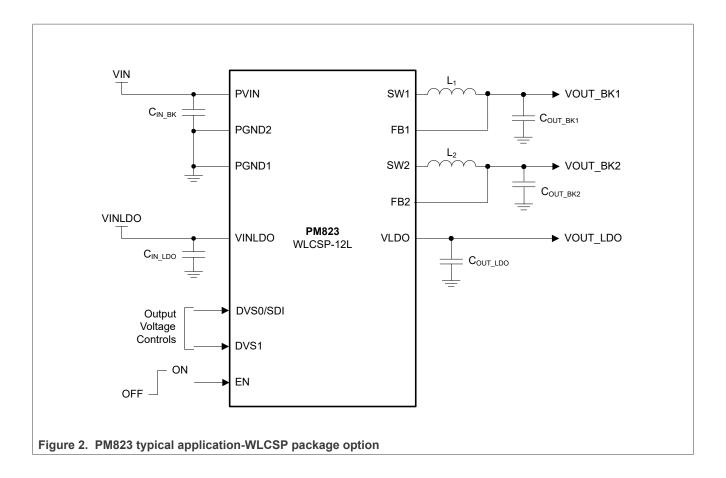

The PM823 is an efficient low-cost power regulator. It consists of two 1.5 A buck regulators and one 525 mA LDO. The LDO can be powered by the buck converter output (≥1.6 V) to minimize the power loss and simplify the system thermal de-sign.

The PM823 is optimized for module applications. It minimizes the PCB footprint and BOM cost. The PM823 12bump WLCSP package provides the smallest footprint for the state-of-the-art module applications. For general purpose applications, the 24-pin QFN package can meet the low-cost PCB requirements. The QFN package also provides additional functions such as power good outputs.

The PM823 Dynamic Voltage Scaling (DVS) feature supports the latest SoC and processor power control scheme. The PM823 also supports Adaptive Voltage Scaling (AVS). The serial interface can be used to program the device to meet different application requirements.

#### **Features**

- Supports 2.7 V~5.5 V operating voltage

- Two 1.5 A synchronous buck converters

- · Single LDO supports up to 525 mA

- Ultra low 15 µA sleep current

- · 3 MHz switching frequency

- · High output voltage accuracy

- Supports both DVS and AVS

- · Single wire proprietary serial interface

#### Package options

- WLCSP-12 lead (0.35 mm ball pitch)

- QFN-24 lead (0.5 mm pin pitch)

#### **Applications**

- IoT devices

- · Wi-Fi modules

- · Smart home devices

- · Cameras, printers

- Smart appliances

- · Wi-Fi hubs, Access Points (APs)

- · Set top boxes

Dual Synchronous 1.5A/1.5A Step-down Buck Regulators with 525 mA LDO

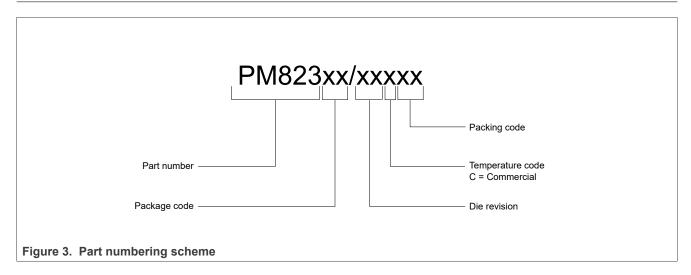

# 2 Ordering information

The standard ordering part numbers for the respective solutions are the following:

Table 1. Part order options

| Part order number             | Buck1 output voltage | Buck2 output<br>voltage | LDO output<br>voltage | Package type |

|-------------------------------|----------------------|-------------------------|-----------------------|--------------|

| PM823UK/A0CZ (Tape and Reel)  | 1.1V                 | 2.2V                    | 1.8V                  | 12-pad WLCSP |

| PM823HN/A0CHP (Tape and Reel) | 1.1V                 | 2.2V                    | 1.8V                  | 24-pin QFN   |

**Note:** Based on Marvell's 88PG823 RMA history, no RMA will be accepted except manufacturing defects. Device provided AS-IS and support limited to NXP Wi-Fi/Bluetooth system-related questions.

Dual Synchronous 1.5A/1.5A Step-down Buck Regulators with 525 mA LDO

# 3 Signal description

# 3.1 Pin configuration

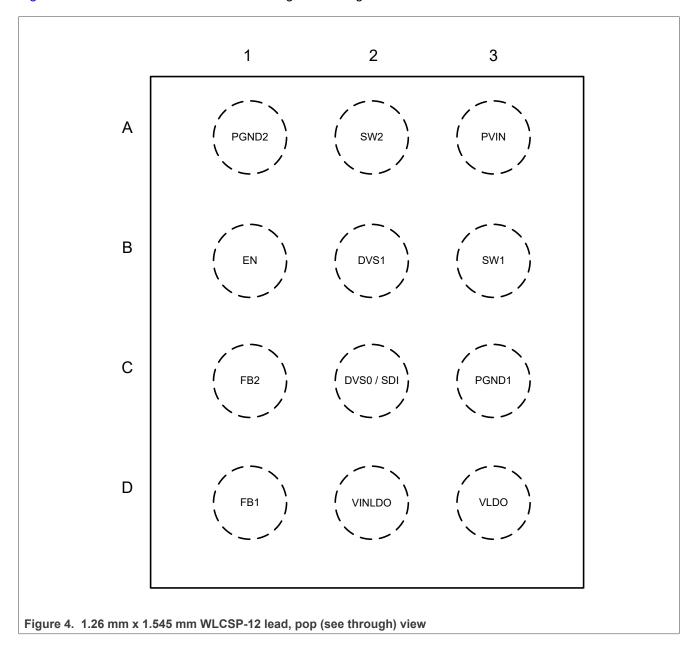

### 3.1.1 12-lead WLCSP configuration

Figure 4 shows PM823 12-lead WLCSP configuration diagram.

Dual Synchronous 1.5A/1.5A Step-down Buck Regulators with 525 mA LDO

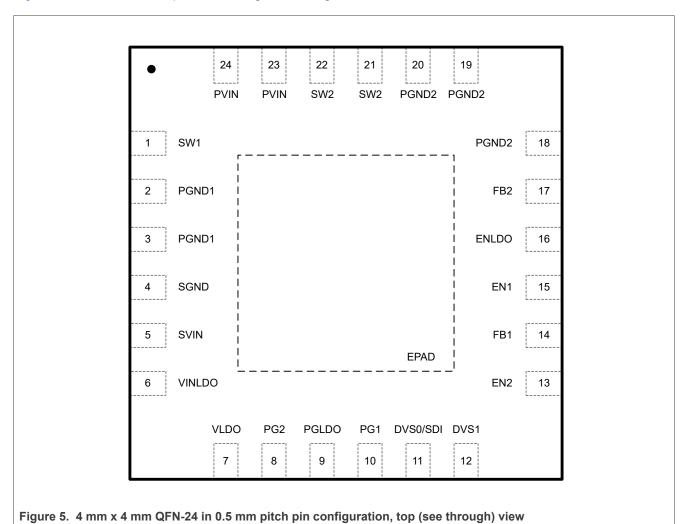

### 3.1.2 24-pin QFN configuration

Figure 5 shows PM823 24-pin QFN configuration diagram.

# 3.2 Pin descriptions

Table 3 shows the pin description details for PM823.

Table 2. Pin types

| Pin type | Description    |

|----------|----------------|

| I        | Input          |

| I/O      | Input / Output |

| GND      | Ground         |

| NC       | No Connection  |

| S        | Supply         |

| 0        | Output         |

PM823

Table 3. Pin description

| Pin<br>number | in description | Pin name Pin type |     | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|---------------|----------------|-------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WLCSP         | QFN            |                   |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| A1            | 18, 19, 20     | PGND2             | GND | Power ground for Buck2 regulator  It must be connected to the negative terminals of the input and output capacitors  All PGND pins must be connected to SGND, EPAD, and make a star connection to system ground  Do not float any PGND pin                                                                                                                                                                                                                                   |

| A2            | 21, 22         | SW2               | 0   | <ul> <li>Switch node for Buck2 regulator</li> <li>Internally connected to the drains of the high side and low side MOSFETs</li> <li>Connect to the external inductor</li> <li>When the switching regulator is disabled, the SW node is high-impedance</li> <li>If the step-down regulator 2 is not in use, float this pin</li> </ul>                                                                                                                                         |

| A3            | 23, 24         | PVIN              | S   | Switching regulator power input  Power input voltage. Internally connected to the source of the high side MOSFET.  Connect a ceramic input capacitor or an equivalent low ESR input capacitor between PVIN and PGND. Place it as close as possible to PVIN and PGND pins. See Section 8 "Application information".  The voltage between SVIN and PVIN should be equal to 50mV or less  All PVIN pins must be connected to the same voltage source  Do not float any PVIN pin |

| B1            | N/A            | EN                | I   | <ul> <li>Enable Input for all regulators</li> <li>Logic high enables regulators and logic low disables regulators</li> <li>See Section 4 "Electrical specifications" for detailed logic high and logic low specifications</li> <li>When not in use, connect this pin to GND or connect a 0Ω resistor to GND</li> <li>Do not float this pin</li> </ul>                                                                                                                        |

| B2            | 12             | DVS1              | I   | Dynamic voltage scaling control 1  This digital input is used to select one of the three operating modes. See Section 5.6 "Operating modes" output voltage settings for mode selection.  Do not float this pin                                                                                                                                                                                                                                                               |

| В3            | 1              | SW1               | 0   | Switch node for buck1 regulator  Internally connected to the drains of the high side and low side MOSFETs  Connect to the external inductor  When the switching regulator is disabled, the SW node is high impedance  If Step-down Regulator 1 is not in use, float this pin                                                                                                                                                                                                 |

| C1            | 17             | FB2               | I   | Buck2 regulator output voltage sense feedback  Connect this pin to the output capacitor  This pin senses the output voltage of the switching regulator  Do not float this pin                                                                                                                                                                                                                                                                                                |

Table 3. Pin description...continued

| Pin    |      |          |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

|--------|------|----------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| number | 0.5  | Pin name | Pin type | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| WLCSP  | QFN  |          |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| C2     | 11   | DVS0/SDI |          | <ul> <li>Dynamic voltage scaling control 0 / serial data input</li> <li>This digital input pin has two functions</li> <li>If DVS1=0, this pin is used as DVS0 input</li> <li>If DVS1=1, this pin becomes the one wire serial interface input</li> <li>Input data into this pin is used to program the output voltage (see Section 5.2 "Serial interface (1-wire)")</li> <li>When not in use, connect this pin to GND or connect a 0Ω resistor to GND</li> <li>Do not share this pin with other serial interface pins</li> <li>Do not float this pin</li> </ul> |  |  |

| C3     | 2, 3 | PGND1    | GND      | Power ground for Buck1 regulator  This pin must be connected to the negative terminals of the input and output capacitors  All PGND pins must be connected to SGND, EPAD, and make a star connection to system ground  Do not float this pin                                                                                                                                                                                                                                                                                                                   |  |  |

| D1     | 14   | FB1      | I        | Buck1 regulator output voltage sense feedback  Connect this pin to the output capacitor  This pin senses the output voltage of the switching regulator  Do not float this pin                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| D2     | 6    | VIN-LDO  | S        | <ul> <li>LDO power supply</li> <li>This is the power supply input for the LDO Regulator</li> <li>Connect a ceramic input capacitor or an equivalent low ESR input capacitor between this pin and the ground plane. Place it as close as possible to this pin and the ground plane. See <a application="" href="Section 8" information"="">Section 8 "Application information"</a>.</li> </ul>                                                                                                                                                                  |  |  |

| D3     | 7    | VLDO     | 0        | <ul> <li>LDO output</li> <li>This pin is the output of the LDO</li> <li>Connect a ceramic output capacitor or an equivalent low ESR output capacitor between this pin and the ground plane. Place it as close as possible to this pin and the ground plane. See <u>Section 8 "Application information"</u>.</li> </ul>                                                                                                                                                                                                                                         |  |  |

| N/A    | 4    | SGND     | GND      | <ul> <li>Signal ground</li> <li>This pin must be connected to SGND, all PGNDx pins, and make a star connection to system ground</li> <li>Do not float this pin</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| N/A    | 5    | SVIN     | S        | <ul> <li>Signal input voltage</li> <li>This is the input voltage pin to the internal circuitry. See Section 4.4  "Electrical characteristics" for input voltage range.</li> <li>Connect a decoupling ceramic capacitor or an equivalent low ESR decoupling capacitor between SVIN and SGND and position it as close as possible to the IC. See Section 8 "Application information".</li> <li>The voltage between SVIN and PVIN should be equal to 50mV or less</li> <li>Do not float this pin</li> </ul>                                                       |  |  |

| N/A    | 8    | PG2      | 0        | Buck2 regulator power good output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

Table 3. Pin description...continued

| Pin    | iii uescripti | Oncontinued |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

|--------|---------------|-------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| number |               | Pin name    | Pin type | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| WLCSP  | QFN           |             |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

|        |               |             |          | <ul> <li>This pin is an open-drain output</li> <li>Connect a 100kΩ pull-up resistor from this pin to VOUT or a logic rail that is equal to or less than SVIN</li> <li>The PG is held low when the output voltage is outside its regulation band and goes high after the output voltage is within regulation</li> <li>When not in use, float this pin</li> <li>In shutdown, the PG will be actively low</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| N/A    | 9             | PGLDO       | 0        | <ul> <li>LDO power good</li> <li>This pin is an open-drain output</li> <li>Connect a 100kΩ pull-up resistor from this pin to VOUT or a logic rail that is equal to or less than SVIN</li> <li>The PG is held low when the output voltage is outside its regulation band and goes high after the output voltage is within regulation</li> <li>When not in use, float this pin</li> <li>In shutdown, the PG will be actively low</li> </ul>                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| N/A    | 10            | PG1         | 0        | <ul> <li>Buck1 regulator power good output</li> <li>This pin is an open-drain output</li> <li>Connect a 100kΩ pull-up resistor from this pin to VOUT or a logic rail that is equal to or less than SVIN</li> <li>The PG is held low when the output voltage is outside its regulation band and goes high after the output voltage is within regulation</li> <li>When not in use, float this pin</li> <li>In shutdown, the PG will be actively low</li> </ul>                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| N/A    | 13            | EN2         | I        | <ul> <li>See Section 5.4 "Power-up sequence" to determine which part numbers have power sequences versus those that do not</li> <li>For part numbers with a power sequence in the QFN-24 package, EN1, EN2, and ENLDO pins need to be connected together. Any logic high from EN1, EN2, and ENLDO pins enables all regulators. EN1, EN2, and ENLDO need to have logic low to disable all regulators. User can not individually enable or disable each stepdown regulator for parts with a power sequence</li> <li>For part numbers without a power sequence, logic high for this pin enables Step-down Regulator 2. Logic low for this pin disables Stepdown Regulator 2</li> <li>When not in use, connect this pin to GND or connect a 0Ω resistor to ground</li> <li>Do not float this pin</li> </ul> |  |  |  |

| N/A    | 15            | EN1         | I        | Buck1 enable input  • See Section 5.4 "Power-up sequence" to determine which part numbers have power sequences versus those that do not  • For part numbers with a power sequence in the QFN-24 package, EN1, EN2, and ENLDO pins need to be connected together. Any logic high from EN1, EN2, and ENLDO pins enables all regulators. EN1, EN2, and ENLDO need to have logic low to disable all regulators. User can not individually enable or disable each stepdown regulator for parts with a power sequence                                                                                                                                                                                                                                                                                         |  |  |  |

Table 3. Pin description...continued

| Pin       |    |          |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-----------|----|----------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| number    |    | Pin name | Pin type | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| WLCSP QFN |    |          |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|           |    |          |          | <ul> <li>For part numbers without a power sequence, logic high for this pin enables Step-down Regulator 1. Logic low for this pin disables Step-down Regulator 1</li> <li>When not in use, connect this pin to GND or connect a 0Ω resistor to ground</li> <li>Do not float this pin</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| N/A       | 16 | ENLDO    |          | <ul> <li>See Section 5.4 "Power-up sequence" to determine which part numbers have power sequences versus those that do not</li> <li>For part numbers with a power sequence in the QFN-24 package, EN1, EN2, and ENLDO pins need to be connected together. Any logic high from EN1, EN2, and ENLDO pins enables all regulators. EN1, EN2, and ENLDO need to have logic low to disable all regulators. User can not individually enable or disable each step-down regulator for parts with a power sequence</li> <li>For part numbers without a power sequence, logic high for this pin enables the LDO Regulator. Logic low for this pin disables the LDO Regulator</li> <li>When not in use, connect this pin to GND or connect a 0Ω resistor to ground</li> <li>The voltage on this pin must never be higher than the voltage on the SVIN pin + 0.3V for all conditions</li> <li>Do not float this pin</li> </ul> |

| N/A       | 25 | EPAD     | GND      | <ul> <li>Exposed thermal pad</li> <li>This pin must be connected to SGND, all PGND pins, and make a star connection to system ground. See <u>Section 8 "Application information"</u>.</li> <li>Do not float this pin</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

Dual Synchronous 1.5A/1.5A Step-down Buck Regulators with 525 mA LDO

# 4 Electrical specifications

### 4.1 Absolute maximum ratings

Table 4. Absolute maximum ratings<sup>[1]</sup>

| Parameter                                                                   | Range                                              | Unit |

|-----------------------------------------------------------------------------|----------------------------------------------------|------|

| V <sub>SVIN</sub> to SGND                                                   | -0.3 to +6.0                                       | V    |

| S <sub>VIN</sub>                                                            | V <sub>PVINx</sub> -0.3 to V <sub>PVINx</sub> +0.3 | V    |

| V <sub>PVINx</sub> to PGNDx                                                 | -0.3 to +6.0                                       | V    |

| V <sub>SWx</sub> to PGNDx <sup>[2]</sup>                                    | -0.3 to (V <sub>PVINx</sub> +0.3)                  | V    |

| SGND to PGNDx                                                               | -0.3 to +0.3                                       | V    |

| V <sub>EN</sub> , V <sub>EN_LDO</sub> , V <sub>EN1</sub> , V <sub>EN2</sub> | -0.3 to (V <sub>SVIN</sub> +0.3)                   | V    |

| V <sub>DVS0/SDI</sub> , V <sub>DVS1</sub>                                   | -0.3 to +6.0                                       | V    |

| Maximum junction temperature                                                | 150                                                | °C   |

| Storage temperature range                                                   | -65 to 150                                         | °C   |

<sup>[1]</sup> Exceeding the absolute maximum rating may damage the device.

# 4.2 Recommended operating conditions

Table 5. Recommended operating conditions<sup>[1]</sup>

| Symbol             | Parameter                              | Min | Тур | Max | Unit |

|--------------------|----------------------------------------|-----|-----|-----|------|

| V <sub>PVIN</sub>  | Buck input power voltage               | 2.7 |     | 5.5 | V    |

| V <sub>INLDO</sub> | LDO input power voltage                | 1.6 |     | 5.5 | V    |

| T <sub>JMAX</sub>  | Maximum operating junction temperature |     |     | 125 | °C   |

| $\Theta_{JA}$      | Package thermal resistance (WLCSP-22L) |     | 40  |     | °C/W |

| $\Theta_{JA}$      | Package thermal resistance (QFN-24L)   |     | 50  |     | °C/W |

| T <sub>A</sub>     | Operating ambient temperature range    | -40 |     | 85  | °C   |

<sup>[1]</sup> Specifications over the -40°C to 85°C operating temperature ranges are assured by design, characterization and correlation with statistical process controls.

<sup>[2]</sup> SWx is capable of sustaining -1.0V for less than 50 ns.

Dual Synchronous 1.5A/1.5A Step-down Buck Regulators with 525 mA LDO

# 4.3 External passive components

Table 6. External passive components

| Symbol                                                                        | Parameter           | Conditions                                                                                                                                                                                 | Min    | Тур  | Max | Unit    |

|-------------------------------------------------------------------------------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|------|-----|---------|

| C <sub>IN1_BK</sub> (WLCSP),<br>C <sub>IN1_BK1</sub> , C <sub>IN1_BK2</sub> , | External components | The distance between this capacitor to PVINx and PGNDx must be less than 1 mm. The maximum case size is 0201 (0603 metric). Use capacitor with ±30% tolerance or better.                   | 0.10   | 0.22 |     | μF      |

| C <sub>IN2_BK</sub>                                                           |                     | WLCSP package: Use capacitor with ±30% tolerance or better.                                                                                                                                | 2 x 10 |      |     | μF      |

| C <sub>IN2_BK1</sub> , C <sub>IN2_BK2</sub>                                   |                     | QFN package: Use capacitor with ±30% tolerance or better.                                                                                                                                  | 10     |      |     | μF      |

| C <sub>OUT_BK1</sub> , C <sub>OUT_BK2</sub>                                   |                     | Use capacitor with ±30% tolerance or better.                                                                                                                                               | 22     |      |     | μF      |

| L <sub>BK1</sub> , L <sub>BK2</sub>                                           |                     | Use capacitor with ±30% tolerance or better.                                                                                                                                               |        | 1.0  |     | μН      |

| LC <sub>BK1</sub> , LC <sub>BK2</sub>                                         |                     | The nominal L <sub>BUCKx</sub> x the TOTAL nominal C <sub>OUT</sub> <sub>BUCKx</sub> must not exceed this maximum specification. Use inductor and capacitor with ±30% tolerance or better. |        |      | 60  | μΗ х μF |

| C <sub>IN_LDO</sub>                                                           |                     | Use capacitor with ±30%                                                                                                                                                                    | 10     |      |     | μF      |

| C <sub>OUT_LDO</sub>                                                          |                     | tolerance or better.                                                                                                                                                                       | 4.7    |      | 20  |         |

Dual Synchronous 1.5A/1.5A Step-down Buck Regulators with 525 mA LDO

#### 4.4 Electrical characteristics

Table 7. Electrical characteristics

The following applies unless otherwise noted: Refer to the schematics shown in <u>Section 8.2 "PCB schematics"</u>.  $V_{IN}$  = 3.6V,  $T_A$  = -40°C to +85°C.

| Symbol                                                     | Parameter                                 | Conditions                                                                                                         | Min | Тур | Max | Units |

|------------------------------------------------------------|-------------------------------------------|--------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-------|

| Supply current                                             |                                           |                                                                                                                    |     |     |     |       |

| IQ_MODE1 /<br>IQ_MODE2                                     | Active modes quiescent current            | Active Mode 1 and<br>Mode 2: Buck1 and<br>Buck2 are in PFM mode<br>and LDO is on.<br>V <sub>IN</sub> =5V. No load. |     | 170 |     | μА    |

|                                                            |                                           | Active mode 1 and mode 2: Buck1 and Buck2 are in PWM mode and LDO is on. V <sub>IN</sub> =5V. No load.             |     | 20  |     | mA    |

| I <sub>Q_MODE3</sub>                                       |                                           | Active mode 3: Buck1<br>and Buck2 are in PFM<br>mode and LDO is on.<br>V <sub>IN</sub> = 5V. No load.              |     | 75  |     | μА    |

|                                                            |                                           | Active mode 3: Buck1 and Buck2 are in PWM mode and LDO is on. $V_{IN} = 5V$ . No load.                             |     | 20  |     | mA    |

| I <sub>Q_SLP</sub>                                         | Sleep mode quiescent current              | $V_{DVS0} = V_{DVS1} = 0V.$<br>$V_{IN} = 5V.$ No load.                                                             |     | 15  |     | μА    |

| I <sub>SHDN</sub>                                          | Shutdown current                          | V <sub>ENx</sub> = 0V. V <sub>IN</sub> = 5V                                                                        |     | 1   |     | μA    |

| Buck1 and Buck2                                            | •                                         |                                                                                                                    |     |     |     | 1     |

| V <sub>PVIN</sub>                                          | Power supply input                        |                                                                                                                    | 2.7 |     | 5.5 | V     |

| I <sub>OUT_BK1</sub> / I <sub>OUT_BK2</sub>                | Maximum output current in full power mode |                                                                                                                    | 1.5 |     |     | А     |

| I <sub>OUT_B</sub> -K1_SLP /<br>I <sub>OUT_B</sub> -K2_SLP | Maximum output current in sleep mode      |                                                                                                                    | 10  |     |     | mA    |

| V <sub>OUT_BK1</sub> /<br>V <sub>OUT_BK2</sub>             | Nominal output voltage                    | Programmable                                                                                                       | 0.6 |     | 3.3 | V     |

| RDS <sub>PMOS</sub>                                        | High-side (PMOS) on-<br>resistance        | V <sub>IN</sub> = 3.6V                                                                                             |     | 80  |     | mΩ    |

| RDS <sub>NMOS</sub>                                        | Low-side (NMOS) on-<br>resistance         | V <sub>IN</sub> = 3.6V                                                                                             |     | 40  |     | mΩ    |

| F <sub>SW</sub>                                            | Switching frequency                       |                                                                                                                    |     | 3   |     | MHz   |

| DUTY <sub>MAX</sub>                                        | Maximum duty cycle                        |                                                                                                                    |     |     | 100 | %     |

| V <sub>DC_ACCY</sub>                                       | V <sub>OUT</sub> DC accuracy              |                                                                                                                    |     | ±2  |     | %     |

| $V_{LN\_REG}$                                              | Line regulation                           | V <sub>IN</sub> = 2.7 V to 5.5 V at I <sub>OUT</sub> = 500 mA                                                      |     | 0.1 |     | %/V   |

PM823

All information provided in this document is subject to legal disclaimers.

© 2024 NXP B.V. All rights reserved.

# Dual Synchronous 1.5A/1.5A Step-down Buck Regulators with 525 mA LDO

Table 7. Electrical characteristics...continued

The following applies unless otherwise noted: Refer to the schematics shown in <u>Section 8.2 "PCB schematics"</u>.  $V_{IN}$  = 3.6V,  $T_A$  = -40°C to +85°C.

| Symbol                     | Parameter                                                                          | Conditions                                                    | Min | Тур  | Max | Units              |

|----------------------------|------------------------------------------------------------------------------------|---------------------------------------------------------------|-----|------|-----|--------------------|

| $V_{LD\_REG}$              | Load regulation                                                                    | I <sub>OUT</sub> = 100 mA to<br>1500 mA                       |     | 0.2  | -   | %/A                |

| PGx <sub>VTH</sub>         | BUCKx PG rising threshold                                                          |                                                               |     | 95   |     | %/V <sub>OUT</sub> |

| PGx <sub>HYS</sub>         | BUCKx PG hysteresis                                                                |                                                               |     | 5    |     | %/V <sub>OUT</sub> |

| DV <sub>RAMP_RATE</sub>    | V <sub>OUT</sub> dynamic voltage ramp rate                                         |                                                               |     | 7    |     | mV/μs              |

| LDO                        |                                                                                    |                                                               |     |      |     |                    |

| V <sub>IN_LDO</sub>        | Power supply input                                                                 |                                                               | 1.6 |      | 5.5 | V                  |

| I <sub>OUT_LDO_</sub> -MAX | Maximum output current in full power mode                                          |                                                               | 525 |      |     | mA                 |

| I <sub>OUT_LDO_MIN</sub>   | Minimum LDO load current                                                           |                                                               | 5   |      |     | μA                 |

| I <sub>OUT_LDO_SLP</sub>   | Maximum output current in sleep mode                                               |                                                               | 10  |      |     | mA                 |

| V <sub>OUT_LDO</sub>       | Nominal output voltage                                                             | Programmable (device part number dependent)                   | 1.2 |      | 3.3 | V                  |

| V <sub>LDO_D</sub> -C_ACCY | LDO output accuracy                                                                |                                                               |     | ±2   |     | %                  |

| $V_{DROP}$                 | Dropout voltage                                                                    | V <sub>OUT</sub> = 1.8 V; I <sub>OUT</sub> = 100 mA           |     | 100  |     | mV                 |

| V <sub>LDO_L</sub> -N_REG  | Line regulation                                                                    | V <sub>IN</sub> = 2.7 V to 5.5 V at I <sub>OUT</sub> = 100 mA |     | 0.05 |     | %/V                |

| V <sub>LDO_LD_REG</sub>    | Load Regula-tion                                                                   | I <sub>OUT</sub> = 100 mA to<br>500 mA                        |     | 1    |     | %                  |

| PGLDO <sub>VTH</sub>       | LDO PG rising threshold                                                            |                                                               |     | 95   |     | %/V <sub>OUT</sub> |

| PGLDO <sub>HYS</sub>       | LDO PG hysteresis                                                                  |                                                               |     | 5    |     |                    |

| Fault protection           |                                                                                    | ,                                                             |     |      |     |                    |

| V <sub>UVLO</sub>          | VIN under Vvltage lock-                                                            | VIN increasing                                                |     | 2.35 |     | V                  |

|                            | out                                                                                | Hysteresis                                                    |     | 0.1  |     |                    |

| V <sub>OVP</sub>           | VIN over voltage                                                                   | VIN increasing                                                |     | 5.7  |     | V                  |

|                            | protection                                                                         | Hysteresis                                                    |     | 0.1  |     |                    |

| T <sub>OTS</sub>           | Over-temperature                                                                   | Temperature rising                                            |     | 145  |     | °C                 |

|                            | thermal shutdown                                                                   | Hysteresis                                                    |     | 20   |     |                    |

| Digital input thre         | esholds                                                                            |                                                               |     | I    |     | -1                 |

| V <sub>IH</sub>            | High level input voltage<br>threshold (EN, EN1,<br>EN2, ENLDO, DVS0/<br>SDI, DVS1) | V <sub>SVIN</sub> = 2.5V to 5.5V                              | 1.2 |      |     | V                  |

| V <sub>IL</sub>            | Low level input voltage threshold (EN, EN1,                                        | V <sub>SVIN</sub> = 2.5V to 5.5V                              |     |      | 0.4 | V                  |

PM823

All information provided in this document is subject to legal disclaimers.

© 2024 NXP B.V. All rights reserved.

### Dual Synchronous 1.5A/1.5A Step-down Buck Regulators with 525 mA LDO

Table 7. Electrical characteristics...continued

The following applies unless otherwise noted: Refer to the schematics shown in <u>Section 8.2 "PCB schematics"</u>.  $V_{IN}$  = 3.6V,  $T_A$  = -40°C to +85°C.

| Symbol | Parameter                       | Conditions | Min | Тур | Max | Units |

|--------|---------------------------------|------------|-----|-----|-----|-------|

|        | EN2, ENLDO, DVS0/<br>SDI, DVS1) |            |     |     |     |       |

Dual Synchronous 1.5A/1.5A Step-down Buck Regulators with 525 mA LDO

# 5 Functional description

#### 5.1 Overview

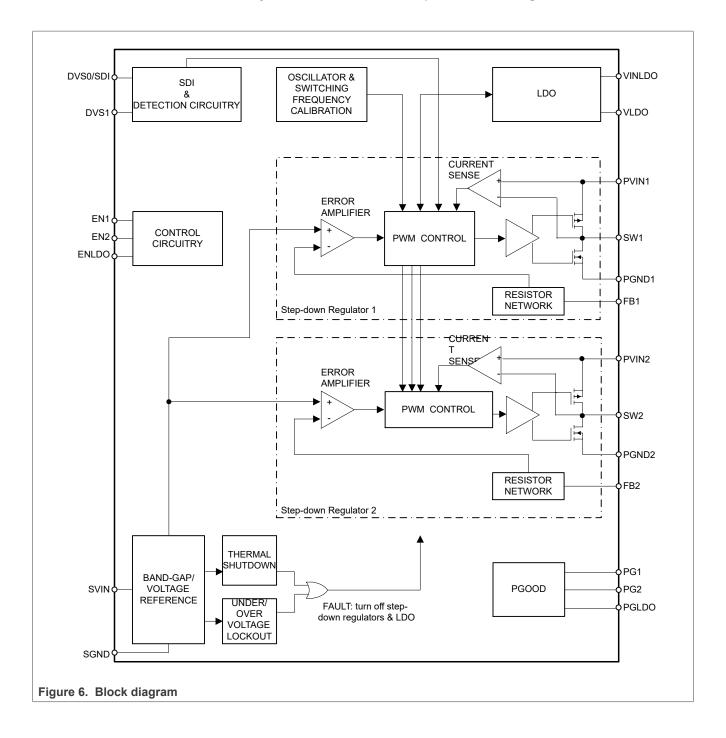

The PM823 is a performant power management regulator as well as a general purpose power management regulator for portable applications. The PM823 includes two step-down switching (Buck) regulators and one Low Dropout (LDO) regulator. The switching step-down regulators utilize a proprietary internally compensated PWM control to regulate its respective output voltages that require no additional external compensation. The PM823 operates from an input voltage range of 2.7V to 5.5V. The LDO regulator can operate with an input voltage ranging from 100 mV above its regulation point to 5.5V. Each of the two switching regulators can deliver a maximum continuous load of 1.5A at 3 MHz switching frequency; while the LDO can deliver a continuous load current of up to 525 mA. Figure 6 shows the PM823 block diagram.

#### Dual Synchronous 1.5A/1.5A Step-down Buck Regulators with 525 mA LDO

# 5.2 Serial interface (1-wire)

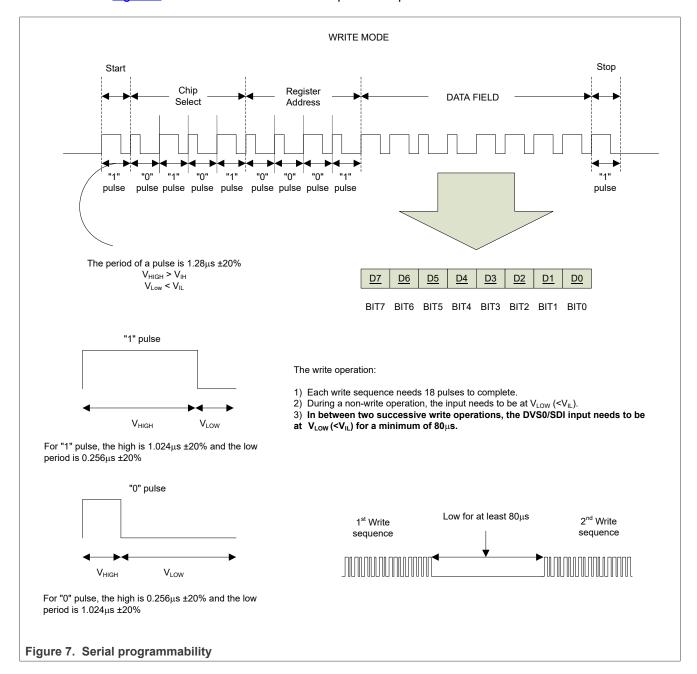

The PM823 uses the 1-wire interface. The input for the serial interface is the DVS0 pin, but this functionality is only enabled when the DVS1 pin is set to a high state. Please note SDI capability is not available in sleep mode as this mode requires DVS0=DVS1=Low. The frequency of the SDI interface is 781.25kHz, and has a 20% tolerance. Figure 7 illustrates the serial interface pulse setup.

Dual Synchronous 1.5A/1.5A Step-down Buck Regulators with 525 mA LDO

#### 5.3 Soft start

The PM823 internally controls the inrush current when the regulator is enabled. This is accomplished by ramping up the desired output voltage based on steps for a predetermined amount of time. Allowing the output voltage to ramp up in this fashion minimizes the current required to charge the output capacitance, therefore limiting the inrush current.

The LDO typical soft start current limit is 50 mA. After the soft start timer has expired (~1 ms), the LDO outputs the full current.

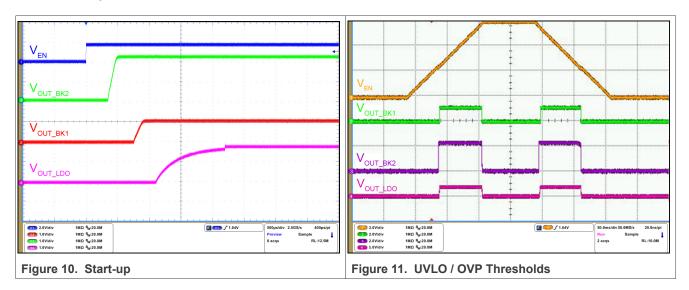

#### 5.4 Power-up sequence

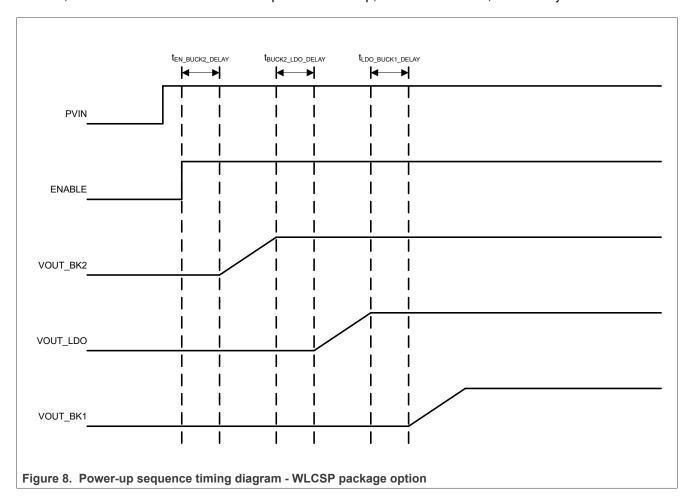

For PM823 with WLCSP package, the EN pin controls the output sequence for all three regulators.

For PM823 with QFN package, it is recommended that EN1, EN2, and ENLDO are connected. Once the part is enabled, Buck2 initializes. After Buck2 completes its start-up, the LDO initializes, followed by Buck1.

Dual Synchronous 1.5A/1.5A Step-down Buck Regulators with 525 mA LDO

# 5.5 Power good

The PM823 contains a power good comparator which pulls low when the output voltage falls below 90% of its regulated value, or when the output voltage is above 95% of its regulated value when the output voltage is rising. The PGOOD output is an open-drain transistor which is off and becomes high impedance when the output voltage is in regulation. This high impedance state allows an external resistor to pull the PGOOD pin high when this transistor is off, or when the buck regulator is disabled via the enable pin.

#### 5.6 Operating modes

The PM823 supports four operating modes selected by the Dynamic Voltage Scaling (DVS) pins as shown in <u>Table 8</u>. Each operating mode provides different power-saving features to meet different application needs. For example, even if the serial interface is not used, the DVS pins are still able to provide the power-saving feature.

Table 8. Operating mode selections

| Operating mode | DVS1 | DVS0 | DVS_EN         | Functional description                                             |

|----------------|------|------|----------------|--------------------------------------------------------------------|

| Active mode 1  | High | SDI  | X (don't care) | Full power mode and the serial interface (pin DVS0) are enabled    |

| Active mode 2  | Low  | High | 1              | Full power mode is enabled, but the serial interface is disabled   |

| Active mode 3  | Low  | High | 0              | Automatic power-saving mode and the serial interface are disabled  |

| Sleep<br>mode  | Low  | Low  | 1              | Lowest power mode is enabled, and the serial interface is disabled |

The PM823 supports two full-power modes, Active Mode 1 and Active Mode 2. Both full power modes have the same power consumption. The major differences are first that the serial interface is not enabled in Active Mode 2, and second that the buck1 regulator can be programmed with different output voltages in Active Modes 1 and 2 to support different applications.

When the PM823 is set to Active Mode 3, the internal clock automatically turns off during a light load (PFM) condition to reduce the system power consumption, but the output voltage remains the same as in Active Mode 1. Active Mode 3 improves the system power consumption if the serial interface is not used.

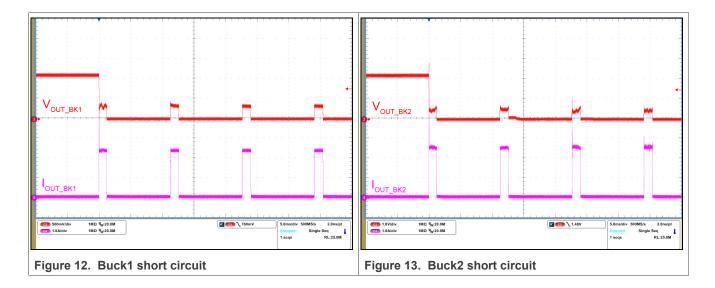

The PM823 also supports the Sleep mode function, which minimizes the system power during a low power mode event. The PM823 quiescent current is reduced to 15 µA during Sleep mode. However, during Sleep mode, the maximum output current for each regulator is limited to 10 mA. If the load current is increased beyond the limit, the over-current protection mechanism kicks in and shuts down the output voltage.

#### 5.7 Sleep mode

The PM823 supports the sleep mode function which saves power when the system is in low power mode. The maximum output current for each regulator is limited to 10 mA. If the load current is increased beyond the sleep mode current limit, the PM823 over-current protection kicks in and shuts down the corresponding output. The DVS0 and DVS1 pins are used to set the PM823 to different operating modes.

Dual Synchronous 1.5A/1.5A Step-down Buck Regulators with 525 mA LDO

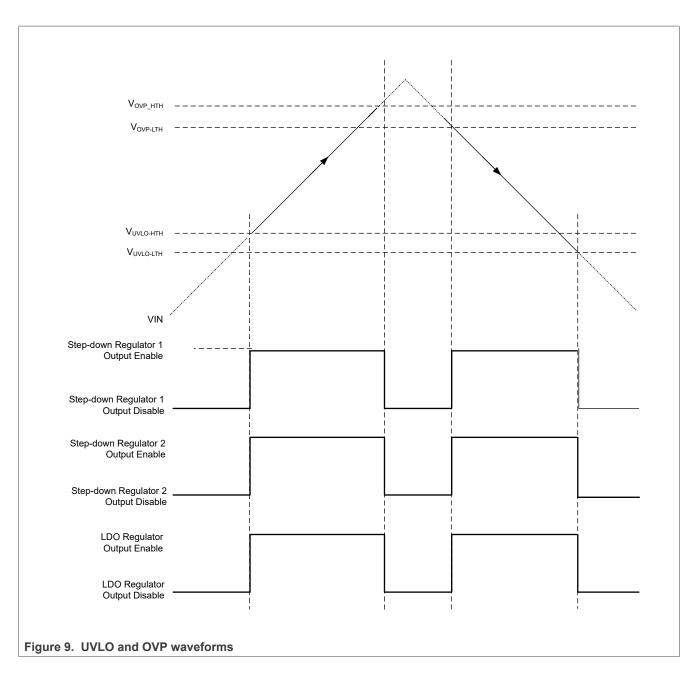

# 5.8 Under voltage lock-out (UVLO)

This feature ensures that both internal MOSFETs for the step-down regulators and for the LDO regulator have adequate voltage levels to operate. When the input voltage is below UVLO low threshold, both MOSFETs for the step-down regulators and for the LDO regulator are off until the input rises above the UVLO high threshold. The switching nodes (SW) for both step-down regulators are in high Z state when the input voltage is less than UVLO high threshold.

# 5.9 Over voltage protection (OVP)

An over-voltage comparator guards against line transient overshoots, as well as other serious conditions that may damage the IC. When the input voltage is above OVP high threshold the output turns off and the switching node (SW) for both step-down regulators are high Z. The device will remain at this state until the input voltage comes back below OVP low threshold.

#### Dual Synchronous 1.5A/1.5A Step-down Buck Regulators with 525 mA LDO

### 5.10 Over-temperature thermal shutdown (OTS)

When the junction temperature exceeds OTS high threshold, the thermal shutdown circuitry disables the PM823. The device is enabled again once the junction temperature is below OTS low threshold.

Dual Synchronous 1.5A/1.5A Step-down Buck Regulators with 525 mA LDO

# 6 Functional characteristics

See Section 8.2 "PCB schematics". The following applies unless otherwise noted: T<sub>A</sub> = 25°C,

$V_{IN}$  = 5V,  $V_{OUT\_BK1}$  = 1.1V,  $V_{OUT\_BK2}$  = 2.2V, and  $V_{OUT\_LDO}$  = 1.8V.

#### 6.1 Start-up waveforms

Dual Synchronous 1.5A/1.5A Step-down Buck Regulators with 525 mA LDO

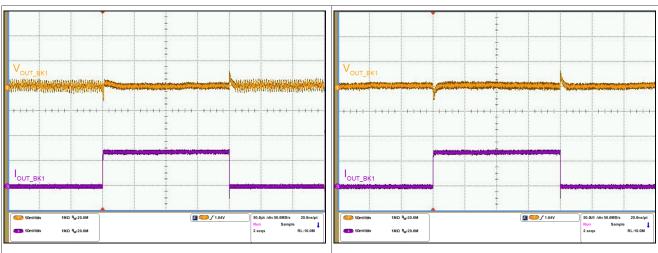

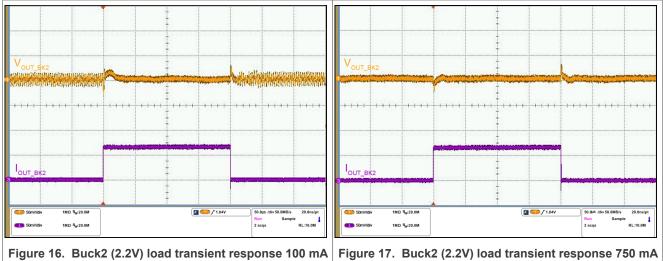

#### 6.2 Load transient waveforms

Figure 14. Buck1 (1.1V) load transient response 100 mA to 750 mA

Figure 15. Buck1 (1.1V) load transient response 750 mA to 1.5A

to 750 mA

to 1.5A

#### Dual Synchronous 1.5A/1.5A Step-down Buck Regulators with 525 mA LDO

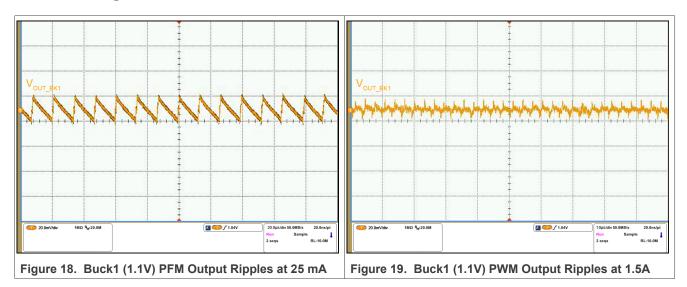

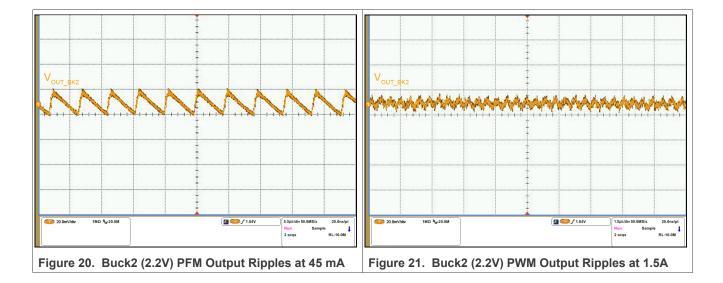

# 6.3 Switching waveforms

Dual Synchronous 1.5A/1.5A Step-down Buck Regulators with 525 mA LDO

# **Typical characteristics**

Unless otherwise noted, the following typical scope photographs were taken using the test circuits shown in Section 8.2 "PCB schematics" at T<sub>A</sub> = 25°C.

Figure 22. Buck1 (1.1V) efficiency vs output current WLCSP-12

Figure 23. Buck2 (2.2V) efficiency vs output current WLCSP-12

Figure 24. Buck1 (3.3V) efficiency vs output current QFN-24

Figure 25. Buck2 (1.8V) efficiency vs output current QFN-24

Figure 26. Buck1 (1.1V) output voltage vs output current Figure 27. Buck2 (2.2V) output voltage vs output current WLCSP-12

WLCSP-12

QFN-24

Figure 28. Buck1 (3.3V) output voltage vs output current Figure 29. Buck2 (1.8V) output voltage vs output current QFN-24

Figure 30. Buck1 output voltage vs input voltage WLCSP-12

Figure 31. Buck2 Output Voltage vs Input Voltage WLCSP-12

(BK1=1.1V, BK2=2.2V, LDO=1.8V,  $V_{INLDO}$  connect to  $V_{INBUCK}$ )

Figure 32. Quiescent Current vs Input Voltage For Active Mode 3

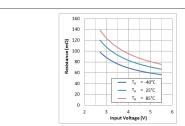

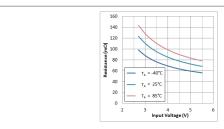

Figure 33. Buck1 high side  $R_{DS(ON)}$  vs. input voltage WLCSP-12

Figure 34. Buck2 high side  $R_{\text{DS(ON)}}$  vs. input voltage WLCSP-12

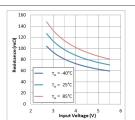

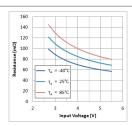

Figure 35. Buck1 low side  $R_{\text{DS(ON)}}$  vs. input voltage WLCSP-12

Figure 36. Buck2 low side  $R_{DS(ON)}$  vs. input voltage WLCSP-12

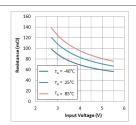

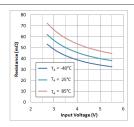

Figure 37. Buck1 high side  $R_{DS(ON)}$  vs. input voltage QFN-24

Figure 38. Buck2 high side  $R_{\text{DS(ON)}}$  vs. input voltage QFN-24

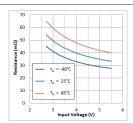

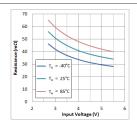

Figure 39. Buck1 low side  $R_{DS(ON)}$  vs. input voltage QFN-24

Figure 40. Buck2 low side  $R_{DS(ON)}$  vs. input voltage QFN-24

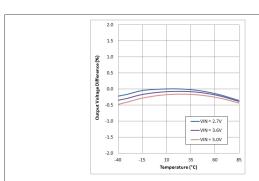

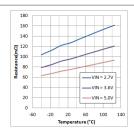

Figure 41. Buck1 Output Voltage Error vs Temperature

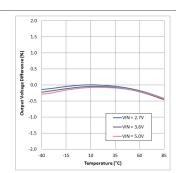

Figure 42. Buck2 Output Voltage Error vs Temperature

(BK1=1.1V, BK2=2.2V, LDO=1.8V,  $V_{INLDO}$  connect to  $V_{INBUCK}$ )

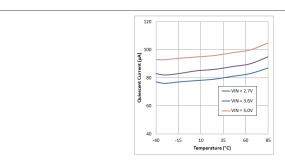

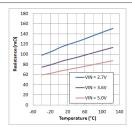

Figure 43. Quiescent current vs temperature for active mode 3

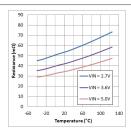

Figure 44. Buck1 high side  $R_{DS(ON)}$  vs. temperature WLCSP-12

Figure 45. Buck2 high side  $R_{DS(ON)}$  vs. temperature WLCSP-12

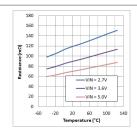

Figure 46. Buck1 low side  $R_{DS(ON)}$  vs. temperature WLCSP-12

Figure 47. Buck2 low side  $R_{DS(ON)}$  vs. temperature WLCSP-12

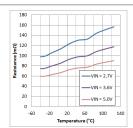

Figure 48. Buck1 high side  $R_{DS(ON)}$  vs. temperature QFN-24

Figure 49. Buck2 high side  $R_{DS(ON)}$  vs. temperature QFN-24

Figure 50. Buck1 low side  $R_{DS(ON)}$  vs. temperature QFN-24

Figure 51. Buck2 low side  $R_{DS(ON)}$  vs. temperature QFN-24

Dual Synchronous 1.5A/1.5A Step-down Buck Regulators with 525 mA LDO

# 8 Application information

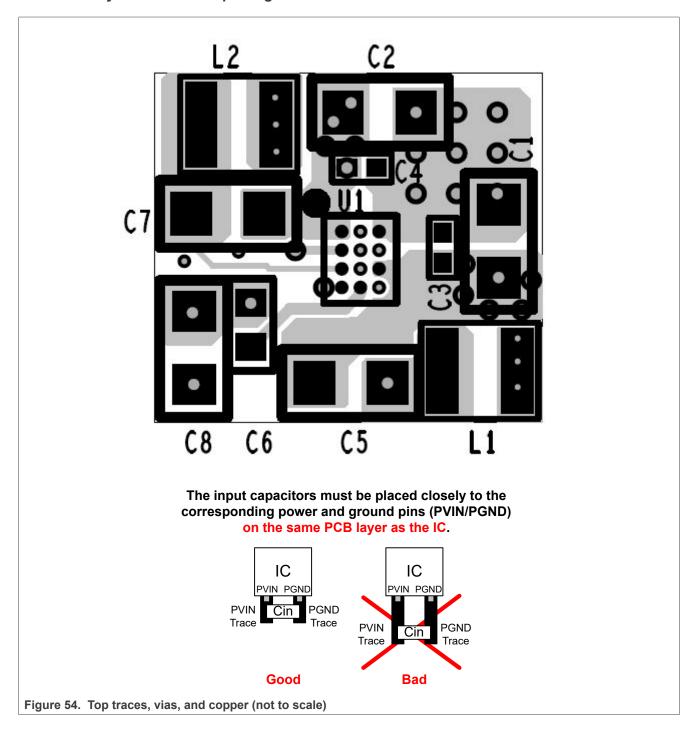

#### 8.1 PC board layout considerations and guidelines

Caution: To avoid abnormal noise and operating behavior follow these layout recommendations.

The PC board layout is very critical in any switching converter application. An improper layout can contribute to system instability, excessive EMI (electromagnetic interference), and high switching loss. Follow these basic guidelines to assure a good PCB layout:

- 1. Copy these layout guidelines within this section as much as possible including the use of the recommended BOM

- 2. Before importing the net list into the layout tool, it is highly recommended to go through the board floor planning phase (the process defining the general location of components on the blank PCB before drawing in any traces).

- a. It is highly recommended to allocate 40% or more of the layout schedule to dedicate for floor planning of the board.

- b. Here are some of the questions that are commonly derived from the floor planning phase. Where to place the SOC on the board?

- On the top or bottom layer?

- In the center?

- c. After deciding where to place the SOC, the next step is to place the power management IC for the core voltage of the SOC.

- d. The optimum position to place the power management IC is on the same layer as the SOC. The output voltage of the power management IC should be close to the input voltage of the SOC.

- e. Continue this floor planning phase for the rest of the voltage rails before starting to layout the board.

- 3. ATTENTION: Before starting to route any traces and after choosing where to place the power management IC on the board, the next step is to place the input capacitors.

- a. Place input capacitor for the SVIN and SGND pins on the same layer as the IC.

- b. Then, place input capacitor for the PVIN and PGND pins on the same layer as the IC.

- c. Next, place the negative terminal for the output capacitors next to the negative terminal of the input capacitors.

- d. See Section 4.4 "Electrical characteristics " for the recommended input and output capacitor values.

- e. See <u>Section 4.4 "Electrical characteristics"</u> for the recommended distance between the IC and the input and output capacitors.

- f. **Do not place the inductor before placing the capacitors.** The input capacitors placement is the most crucial for proper operation. The AC current circulating through the input capacitors, loop (LP1), is a square wave with rise and fall times as fast as 8ns (typical) with slew rates being as high as 300µA/µs (typical). At these fast slew rates, stray and parasitic PCB inductance can generate voltage spikes as high as 3V per inch of the PCB trace;

- $V_{IND} = L * di/dt.$

- g. Keep loop 2 (LP2) as small as possible and connect the negative terminal of the output capacitor as close to the negative terminal of the input capacitor as possible.

- 4. The input capacitors for the SVIN and PVIN pins need to be Ceramic or equivalent low ESR capacitor.

- a. Do not replace the Ceramic input or output capacitors with Tantalum capacitors.

- b. Any type of capacitor can be placed in parallel with the input capacitor as long as the Ceramic input capacitor is placed next to the IC. If Tantalum input capacitors are used, it must be rated for switching regulator applications and the operating voltage must be de-rated by 50%.

- c. Any type of capacitor can be placed in parallel with the output capacitor.

PM82

- d. Low-ESR capacitors like the POSCAP from Sanyo can replace the Ceramic output capacitors as long as the capacitor value is the same or greater. Note that Ceramic capacitors provide the lowest noise and smallest foot print solution.

- 5. Use planes for the ground, input and output power to maintain good voltage filtering and to keep power losses low. If there is not enough space to place a power plane for the input sup-ply, then the input supply trace must be at least 3/8 of an inch wide.

- 6. Keep the switching and all sensitive traces away from the fast dv/dt to minimize capacitive coupling effects.

Dual Synchronous 1.5A/1.5A Step-down Buck Regulators with 525 mA LDO

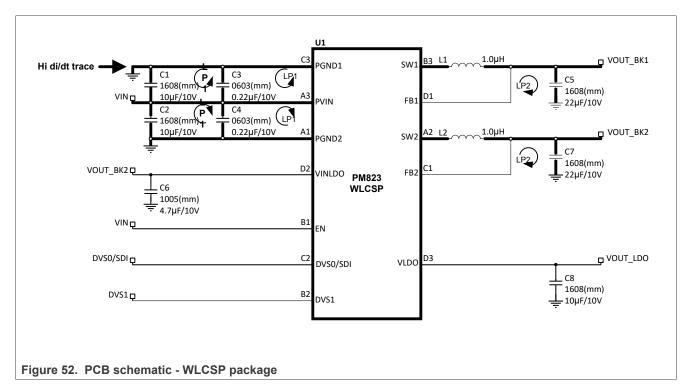

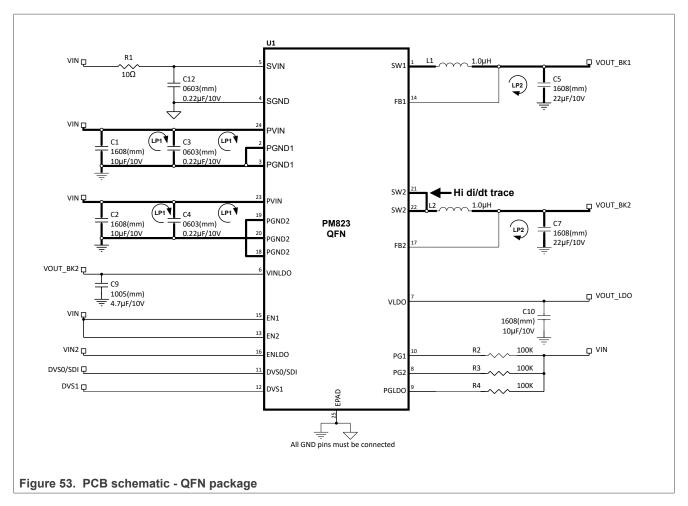

#### 8.2 PCB schematics

#### Notes:

- For C3 and C4, can use 0.1 μF but it is best to use maximum capacitance for the 0603(mm)/0201(in) case size. For example, 0.22 μF is available 0603(mm)/0201(in) size.

- For all capacitors, use the highest voltage rating available for the case size. For example, 22 μF is available in 1608(mm)/0603(in) case size with 6.3V and 10V rating. Use 22 μF/10V rating instead of 22 μF/6.3V rating

- See Section 5.4 "Power-up sequence" for the power sequence function

- Do not float DVS/SDI and DVS1 pin.

#### Dual Synchronous 1.5A/1.5A Step-down Buck Regulators with 525 mA LDO

#### Notes:

- For C3 and C4, can use 0.1μF but it is best to use maximum capacitance for the 0603(mm)/0201(in) case size. For example, 0.22μF is available 0603(mm)/0201(in) size

- For all capacitors, use the highest voltage rating available for the case size. For example, 22μF is available in 1608 (mm) / 0603 (in) case size with 6.3V and 10V rating. Use 22μF/10V rating instead of 22μF/6.3V rating

- For EN1, EN2, and ENLDO pins, can connect directly to VIN or through a 100K pull-up resistor if all outputs are turned on at the same time

- If the LDO output voltage comes after the Buck2 output, then connect VIN\_LDO to VOUT2\_BK2. Either have the ENLDO pin connect to VOUT\_BK2 or connect through a 100K pull-up resistor.

- See Section 5.2 "Serial interface (1-wire)" for the SDI function and configuration

- See Section 5.4 "Power-up sequence" for the power sequence function

- Do not float DVS0/SDI and DVS1 pin.

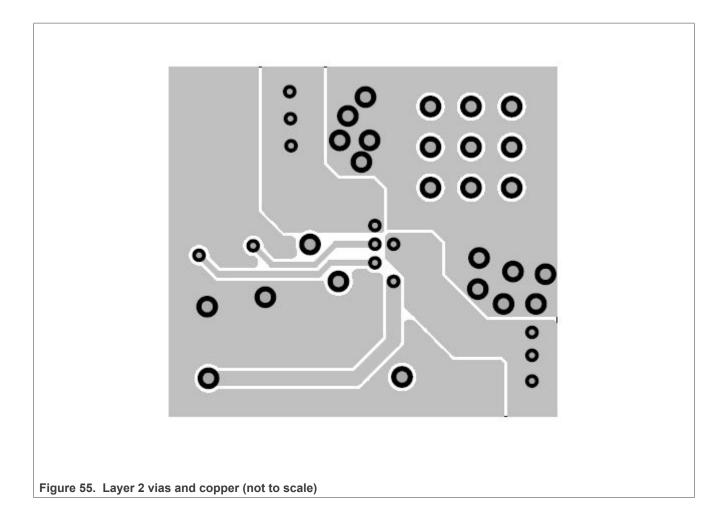

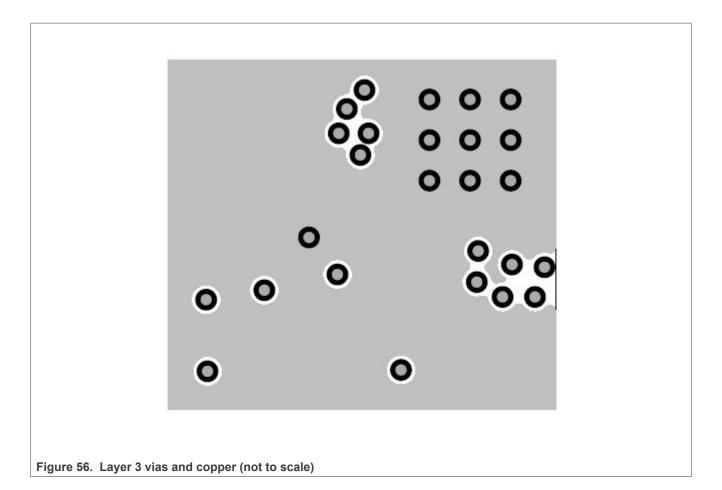

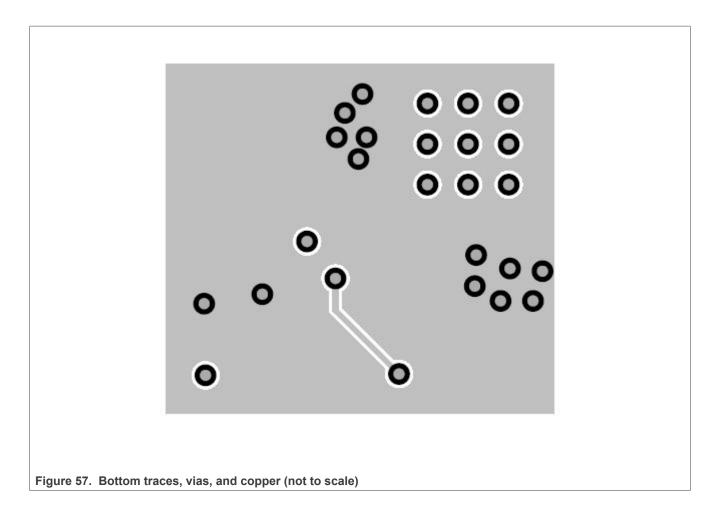

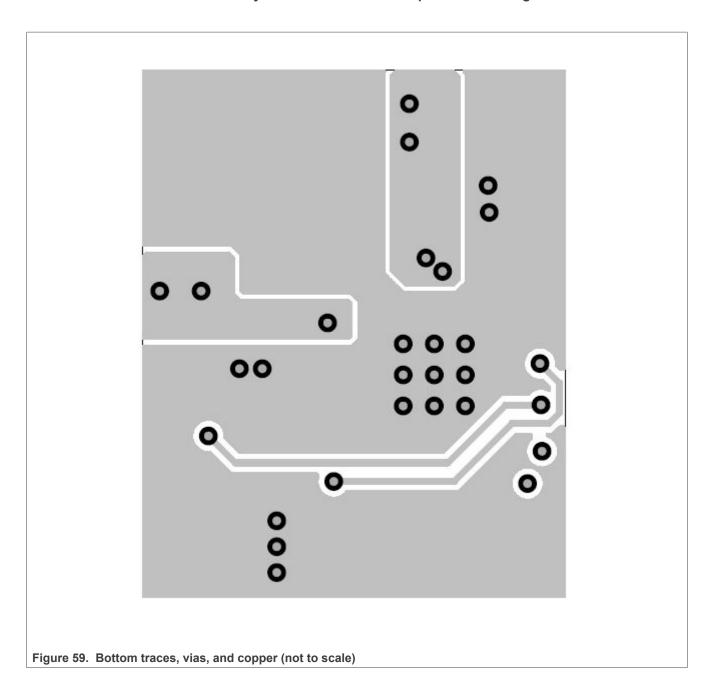

#### 8.3 PCB layout examples

- WLCSP actual board size = 286 mil x 258 mil

- QFN actual board size = 409 mil x 510 mil

- WLCSP total copper layers = 4

- QFN total copper layers = 2

PM823

Dual Synchronous 1.5A/1.5A Step-down Buck Regulators with 525 mA LDO

#### 8.3.1 PCB layout for WLCSP package

Dual Synchronous 1.5A/1.5A Step-down Buck Regulators with 525 mA LDO

### 8.3.2 PCB layout for QFN package

Dual Synchronous 1.5A/1.5A Step-down Buck Regulators with 525 mA LDO

# 8.4 Bill of materials (BOM)

### Note:

Check component datasheets for the latest updates before designing these components in the schematic.

Check the maximum temperature of the applications and maximum heat source that these components will be placed next to. For example, these components might be placed near the SOC and the SOC might act as the heat source. This heat source can have a higher temperature than the ambient temperature. These recommended components are suitable for hand-held and portable applications. Components with high temperature ratings might be needed based on the maximum temperature of the application or the maximum heat source that these components will be subject to.

Table 9. BOM for WLCSP package

| Item | Qty | Ref          | Manufacturer part number | Manufacturer | Description                                                   |

|------|-----|--------------|--------------------------|--------------|---------------------------------------------------------------|

| 1    | 3   | C1,C2,<br>C8 | GRM188R61A106KE69D       | Murata       | CAP CER 10µF 10V ±10% X5R<br>1608(mm) / 0603(in)              |

| 2    | 2   | C3,C4        | GRM033R61A224ME90D       | Murata       | CAP CER 0.22µF 10V ±20% X5R 0603(mm) / 0201(in)               |

| 3    | 2   | C5,C7        | GRM188R61A226ME15        | Murata       | CAP CER 22µF 10V ±20% X5R<br>1608(mm) / 0603(in)              |

| 4    | 1   | C6           | GRM155R61A475MEAA        | Murata       | CAP CER 4.7µF 10V ±20% X5R<br>1005(mm) / 0402(in)             |

| 5    | 2   | L1,L2        | HEI201612A-1R0M-Q8D2     | Chilisin     | HEI201612A Series 1.0μH,<br>L = 2.0mm, W = 1.6mm, H = 1.2mm   |

|      |     |              | MHCD201612A-1R0M-A8SDZ   | Chilisin     | MHCD201612A Series 1.0μH,<br>L = 2.0mm, W = 1.6mm, H = 1.2mm  |

| 6    | 1   | U1           | PM823                    | NXP          | PM823 in WLCSP-12 package with dual synchronous bucks and LDO |

Table 10. BOM for QFN Package

| Item | Qty | Ref           | Manufacturer part number | Manufacturer | Description                                                  |

|------|-----|---------------|--------------------------|--------------|--------------------------------------------------------------|

| 1    | 3   | C1,C2,<br>C10 | GRM188R61A106KE69        | Murata       | CAP CER 10µF 10V ±10% X5R<br>1608(mm) / 0603(in)             |

| 2    | 3   | C3,C4,<br>C12 | GRM033R61A224ME90D       | Murata       | CAP CER 0.22µF 10V ±20% X5R<br>0603(mm) / 0201(in)           |

| 3    | 2   | C5,C7         | GRM188R61A226ME15        | Murata       | CAP CER 22µF 10V ±20% X5R<br>1608(mm) / 0603(in)             |

| 4    | 1   | C9            | GRM155R61A475MEAA        | Murata       | CAP CER 4.7µF 10V ±20% X5R<br>1005(mm) / 0402(in)            |

| 5    | 2   | L1,L2         | HEI201612A-1R0M-Q8D2     | Chilisin     | HEI201612A Series 1.0μH,<br>L = 2.0mm, W = 1.6mm, H = 1.2mm  |

|      |     |               | MHCD201612A-1R0M-A8SDZ   | Chilisin     | MHCD201612A Series 1.0μH,<br>L = 2.0mm, W = 1.6mm, H = 1.2mm |

| 6    | 1   | R1            | RC0402FR-0710RL          | Yageo        | RES 10Ω 1/16W ±1% 0402 SMD                                   |

| 7    | 3   | R2,R3,<br>R4  | RC0402JR-07100KL         | Yageo        | RES 100kΩ 1/16W ±5% 0402 SMD                                 |

| 8    | 1   | U1            | PM823                    | NXP          | PM823 in QFN-24 package with dual synchronous bucks and LDO  |

Dual Synchronous 1.5A/1.5A Step-down Buck Regulators with 525 mA LDO

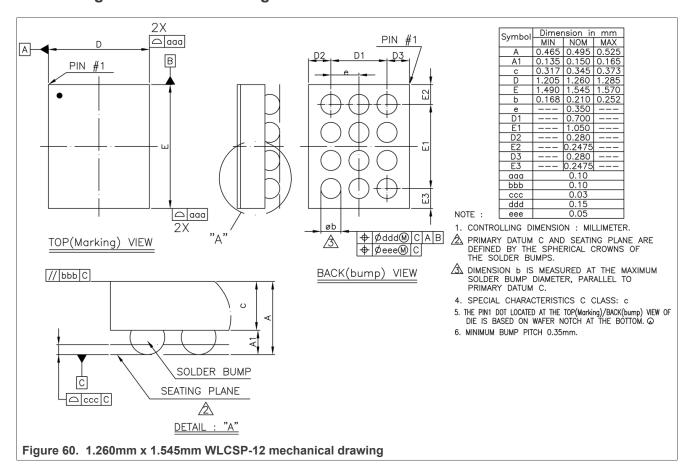

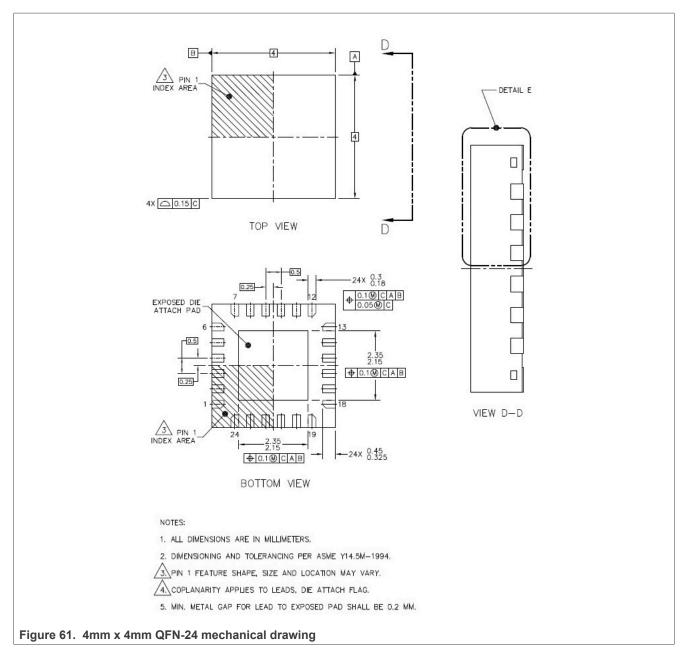

# 9 Package information

# 9.1 Package mechanical drawings

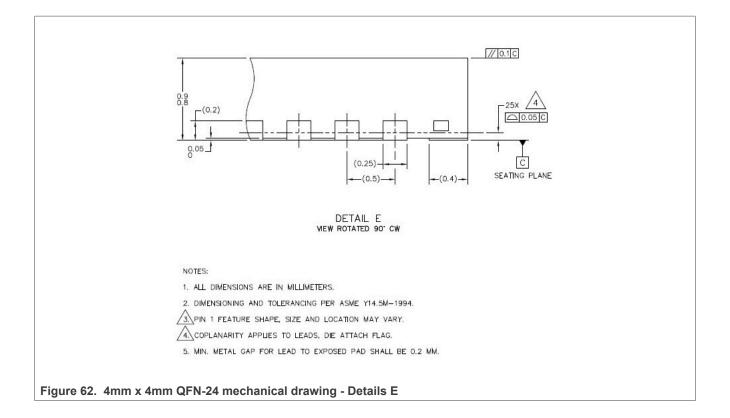

Note: All dimensions in mm. See Section 9.2 "Package markings" for package marking and pin 1 location.

### Dual Synchronous 1.5A/1.5A Step-down Buck Regulators with 525 mA LDO

**Note:** All dimensions in mm. See <u>Section 9.2 "Package markings"</u> for package marking and pin 1 location.

### Dual Synchronous 1.5A/1.5A Step-down Buck Regulators with 525 mA LDO

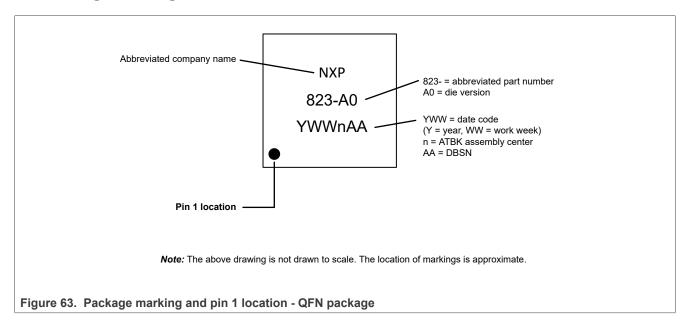

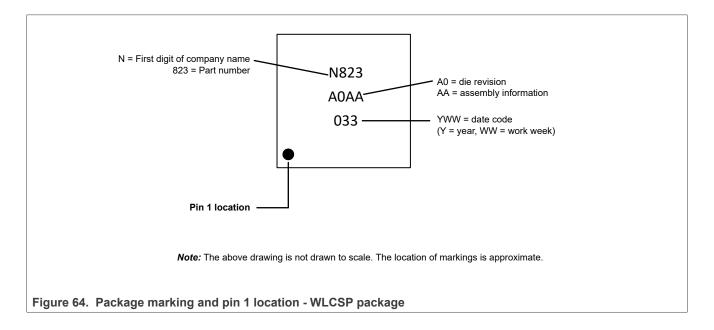

# 9.2 Package markings

Dual Synchronous 1.5A/1.5A Step-down Buck Regulators with 525 mA LDO

# 10 Revision history

Table 11. Revision history

| Document ID | Release date     | Description                                                                                                                                                                                                                                                                                                               |

|-------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PM823 v.5   | 27 February 2024 | CIN 202402023I  • Section 5.6 "Operating modes": removed the reference to internal registers.  • Section DVS output voltage settings: removed.  • Section 5.7 "Sleep mode": removed the reference to DVS register information.  • Section Register sets: removed.                                                         |

| PM823 v.4   | 23 June 2022     | Changed the document confidentiality level from "Company Confidential" to "Public". No changes in the content.                                                                                                                                                                                                            |

| PM823 v.3   | 24 May 2021      | Signal description  • Figure 4 "1.26 mm x 1.545 mm WLCSP-12 lead, pop (see through) view": corrected.  Application information  • Figure 53 "PCB schematic - QFN package": corrected.  Package information  • Section 9.2 "Package markings": updated with the marking of QFN (Figure 63) and WLCSP (Figure 64) packages. |

| PM823 v.2   | 12 May 2021      | Signal description  • Figure 5 "4 mm x 4 mm QFN-24 in 0.5 mm pitch pin configuration, top (see through) view": corrected.                                                                                                                                                                                                 |

| PM823 v.1   | 18 November 2020 | Initial version                                                                                                                                                                                                                                                                                                           |

### Dual Synchronous 1.5A/1.5A Step-down Buck Regulators with 525 mA LDO

# Legal information

#### Data sheet status

| Document status <sup>[1][2]</sup> | Product status <sup>[3]</sup> | Definition                                                                            |  |

|-----------------------------------|-------------------------------|---------------------------------------------------------------------------------------|--|

|                                   |                               | This document contains data from the objective specification for product development. |  |

| Preliminary [short] data sheet    | Qualification                 | This document contains data from the preliminary specification.                       |  |

| Product [short] data sheet        | Production                    | This document contains the product specification.                                     |  |

- [1] Please consult the most recently issued document before initiating or completing a design.

- [2] The term 'short data sheet' is explained in section "Definitions".

- [3] The product status of device(s) described in this document may have changed since this document was published and may differ in case of multiple devices. The latest product status information is available on the Internet at URL <a href="https://www.nxp.com">https://www.nxp.com</a>.

#### **Definitions**

**Draft** — A draft status on a document indicates that the content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included in a draft version of a document and shall have no liability for the consequences of use of such information.

Short data sheet — A short data sheet is an extract from a full data sheet with the same product type number(s) and title. A short data sheet is intended for quick reference only and should not be relied upon to contain detailed and full information. For detailed and full information see the relevant full data sheet, which is available on request via the local NXP Semiconductors sales office. In case of any inconsistency or conflict with the short data sheet, the full data sheet shall prevail.

**Product specification** — The information and data provided in a Product data sheet shall define the specification of the product as agreed between NXP Semiconductors and its customer, unless NXP Semiconductors and customer have explicitly agreed otherwise in writing. In no event however, shall an agreement be valid in which the NXP Semiconductors product is deemed to offer functions and qualities beyond those described in the Product data sheet.

#### **Disclaimers**

Limited warranty and liability — Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information. NXP Semiconductors takes no responsibility for the content in this document if provided by an information source outside of NXP Semiconductors.

In no event shall NXP Semiconductors be liable for any indirect, incidental, punitive, special or consequential damages (including - without limitation - lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory.

Notwithstanding any damages that customer might incur for any reason whatsoever, NXP Semiconductors' aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the Terms and conditions of commercial sale of NXP Semiconductors.

Right to make changes — NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

Suitability for use — NXP Semiconductors products are not designed, authorized or warranted to be suitable for use in life support, life-critical or safety-critical systems or equipment, nor in applications where failure or malfunction of an NXP Semiconductors product can reasonably be expected to result in personal injury, death or severe property or environmental damage. NXP Semiconductors and its suppliers accept no liability for inclusion and/or use of NXP Semiconductors products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.

**Applications** — Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

Customers are responsible for the design and operation of their applications and products using NXP Semiconductors products, and NXP Semiconductors accepts no liability for any assistance with applications or customer product design. It is customer's sole responsibility to determine whether the NXP Semiconductors product is suitable and fit for the customer's applications and products planned, as well as for the planned application and use of customer's third party customer(s). Customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products.

NXP Semiconductors does not accept any liability related to any default, damage, costs or problem which is based on any weakness or default in the customer's applications or products, or the application or use by customer's third party customer(s). Customer is responsible for doing all necessary testing for the customer's applications and products using NXP Semiconductors products in order to avoid a default of the applications and the products or of the application or use by customer's third party customer(s). NXP does not accept any liability in this respect.