# AN13329

# Network subsystem troubleshooting on DPAA2 devices (illustrated with LX2160)

Rev. 0 — 30 August 2021 Application Note

## 1 Introduction

The goal of this document is to familiarize users with the configuration of networking subsystem on the LX2 SoC. With the basic commands for bringing up the network interfaces, it provides debugging techniques for various cases, such as:

# Contents

| 1 | Introduction                   | ′  |

|---|--------------------------------|----|

| 2 | LX2 network interface overview | 2  |

| 3 | Troubleshooting in U-Boot      | 4  |

| 4 | Troubleshooting in Linux OS    | 29 |

| 5 | Additional tips                | 8  |

| 6 | Revision history               |    |

- A component (port, PHY, or MAC) apparently does not work. Link is down on the PHY interface, packets are dropped at the DPNI level, there is no link at PCS/SerDes, or packets are not received by the MAC.

- There is a minimal software infrastructure. Take U-Boot for example, in which the Ethernet ports should successfully send/receive packets to/from a remote peer but, based on the information captured at the other side, no packets are sent out from the LX2 device or/and the network interface from the LX2 does not receive any frames.

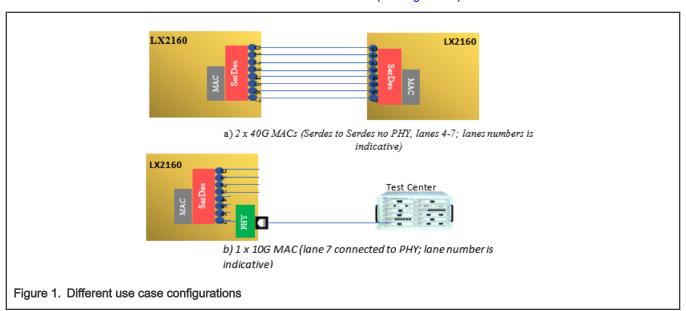

The different LX2 setups that were used for showcasing are composed of RDBs and internal development platforms. The internal development platforms are more flexible in many ways. They were chosen, because it is possible to cover scenarios such as connecting two MACs from SerDes to SerDes without any PHY in between. On the RDB, this cannot be achieved (see Figure 1.a). The RDB is used in scenarios where the MAC is connected to a PHY (see Figure 1.b).

The reader should have a minimal background on the networking architecture for the Linux OS and basic knowledge on the DPAA2 infrastructure. For more details about the components of the DPAA2, see the *DPAA2 User Manual* (document DPAA2UM).

NOTE

The setup in Figure 1.b (RDB boards) may differ in a custom design. The 10G MAC can be connected directly (SerDes to SerDes) to another 10G MAC without a PHY.

# 2 LX2 network interface overview

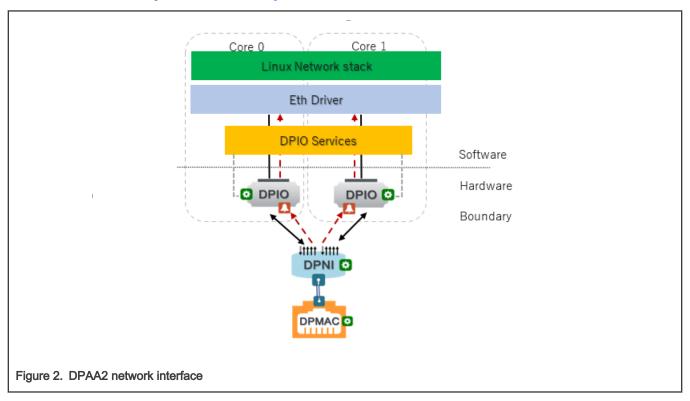

The network interface configuration is shown in Figure 2.

In Figure 2, the ingress and egress pipelines for a packet can be summarized as follows:

#### · On ingress:

A packet is received from the line side and reaches into the FIFO of the DPMAC. The WRIOP port (DPNI), <u>parses and classifies</u> the frame, <u>transfers it</u> into a memory buffer (in the external system memory) from a buffer pool (DPBP) assigned to the DPNI, and <u>enqueues it</u> to one of the Rx queues configured for the interface. (in Figure 2, the frame can be consumed either by Core 0 or Core 1, depending on the classification result. A maximum of 16 cores can be configured for a network interface on the LX2).

#### · On egress:

A packet is <u>enqueued</u> into one of the Tx queues available (the number of TX queues is equal to the number of RX queues) by one of the cores. The packet is <u>dequeued</u> by the WRIOP (DPNI), <u>transferred</u> from the system memory into the WRIOP memory, and sent to the DPMAC. The same memory buffer, containing the frame, is <u>enqueued</u> into a TX confirmation queue. From this queue, the core that sent the frame earlier (or another core) dequeues it and releases the buffer back into the DPNI's buffer pool (DPBP).

NOTE

A comprehensive description of the DPAA2 network infrastructure in the Linux OS is here.

The potential issues that you may encounter are:

- · No link at PHY/MAC or PCS/SerDes

- · Packets not received/sent

- · Packets are dropped

The issues must be traced at the PHY <--- >SerDes <--> DPMAC < --- > DPNI levels and very rarely in the DPAA2 ETH driver itself (which is equivalent to the core side).

Application Note 2 / 82

The simplest method to identify the blockage point is to check the counters on each of the above components. Observing the relevant counter incrementation (for example, the ingress\_discarded\_frames counter on the DPNI object) does not always reveal the source of the problem and it sometimes does not even give a clue about the approximate cause.

One approach of debugging is a step by step investigation by setting different loopback modes in various points (MAC, SerDes, PHY, PCS) and checking whether the frame(s) reached the expected level (MAC, DPNI, core). In the case of dropped frame(s), an error queue shall be enabled together with the debug prints. Both the loopback and error queue options may require additional changes in the software layer (U-Boot or Linux OS). These changes are described in this document.

These modes cannot be used if the goal is to check the performance on a port or to ensure that an interface (DPMAC) works according to the specifications of the selected SerDes protocol. For example, the SerDes protocol is SGMII and you try to validate the conversion from SGMII to KX by sending a couple of frames in the U-Boot.

### 2.1 Interface loopback modes

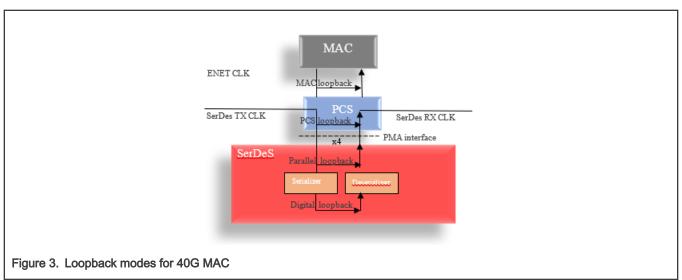

The loopback can be configured on different levels of a network interface:

- MAC

- PCS

- · SerDes (serializer loopback, parallel interface loopback)

- · PHY (if present)

#### **Observations:**

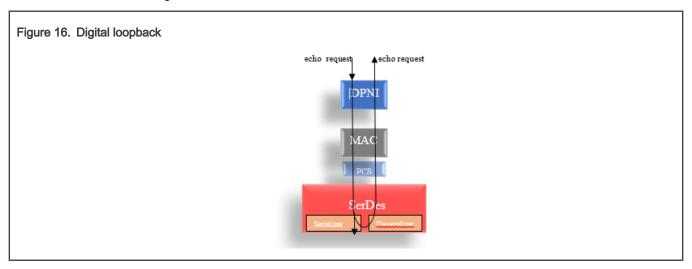

In the digital loopback mode, data is gated in the serializer (RX side only). The RX CLK is derived from the TX CLK.

The digital loopback can be used as a sanity check. If no valid link is observed at the PCS level when enabling this mode, it means that something is wrong at the SerDes level (a hardware issue or an incorrect SerDes configuration).

- In the parallel loopback, two cases can be distinguished:

- (tx\_clk to tx\_clk) "tx\_clk" is used to clock both sides of the FIFO (used to transfer data from TX to RX) and it is bypassed through to the "rx\_clk". On the parallel transmitter side, the data is transmitted and it can reach the remote peer. This mode can be used as a sanity check as well.

- "rx\_clk" is recovered from the input data on the "rx\_p/rx\_n" differential pair inputs. It requires a valid clock from the peer. This mode is not used in this document.

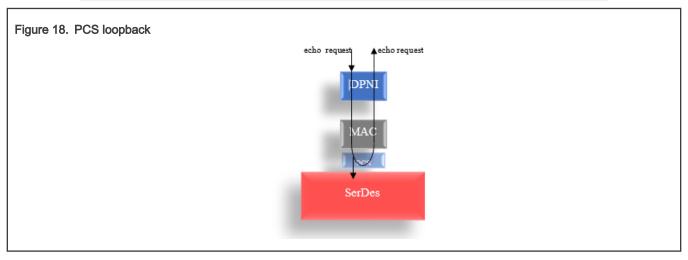

- · In the PCS loopback mode, data is gated in the PCS as follows: On the TX path, data is transmitted normally, whereas on the RX, the data received from the PMA is discarded. The receive clocks must be stable and running at proper

frequencies. If there is no peer, the clock is recovered from the internal PLL. This enables you to test the PCS loopback even if the peer has an invalid configuration.

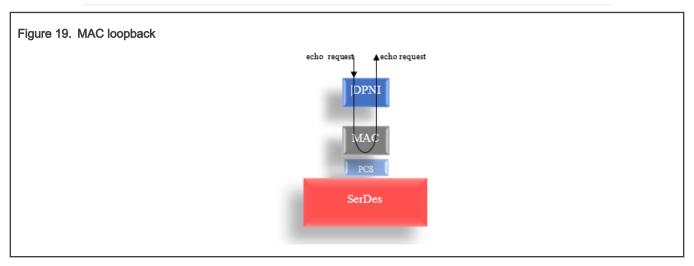

- In the MAC loopback mode, data is gated in the MAC. No data exits the MAC.

- If the investigation of a possible issue (for example, no traffic is received on the DPNI) is carried out in the U-Boot, enabling MAC loopback and PCS loopback may be problematic. The MAC loopback cannot be set without significant changes, because of the network design configuration. The interface is created (the DPMAC is enabled and configured) when a command that sends traffic (for example, ping) is executed from the CLI. It means that the content of the DPMAC COMMAND\_CONFIG register that holds the loopback bit is overwritten every time the ping command is executed. The PCS loopback configured for DPMACs in the SGMII/QSGMII mode is overwritten as well, with two exceptions: USXGMII and XFI. In these two modes, the PCS content is not overwritten during the DPMAC enablement. In this document, the PCS loopback is successfully applied from the U-Boot, because the exemplified interfaces are in the XFI/USXGMII mode.

# 3 Troubleshooting in U-Boot

#### 3.1 Introduction

This section describes the cases in which the traffic is not received on an LX2 port or when it does not reach the destination. The setup is similar to the representation in Figure 1.

Before proceeding with further details on the use cases, here is a short description of the Management Complex (MC).

MC is an NXP provided firmware that runs on the e200 control cores. It implements the DPAA2 object model abstraction logic (hiding all the complexity of the underlying hardware – for example, QBMAN and WRIOP) for the upper software layers that run on the General Purpose Cores (GPPs). MC is a trusted entity and it executes only private trusted code. It can be viewed as a hypervisor slave device. GPP processes do not have direct access to most of the DPAA2 resources. For example, if you want to update the configuration of a frame queue using the QBMAN APIs directly (bypassing the MC API implementation), you cannot access the real frame queue ID and you cannot change the queue configuration. Instead, perform all necessary DPAA2 management using commands to the MC. For more details about MC and DPAA2 object model, see the *DPAA2 User Manual* (document DPAA2UM).

If the MC firmware is not loaded by the boot loader (U-Boot), the DPAA2 network subsystem is not initialized, and it cannot be used in U-Boot or Linux OS (no interfaces are probed).

To use an interface in the U-Boot and later in the Linux OS, load the MC:

```

fsl_mc start mc <firmware_addr> [DPC_addr]

```

The **Data Path Configuration** (DPC) file contains board-specific and system-specific information that may override the default DPAA hardware configuration. See the *DPAA2 User Manual* (document DPAA2UM).

The following are some observations about the DPC:

- It is found at flash offset = 0xe00000/SD card offset = 0x7000.

- · It has a structure similar to the device tree.

- It can be compiled using the "dtc" tool. A blob similar to the DTB is generated.

- It is optional. The MC can boot without it. The U-Boot displays the following warning if no DPC is found: fsl-mc: WARNING: No DPC image found.

- Some examples are here.

Application Note

#### 3.1.1 Displaying the MC log buffer if the firmware cannot start

If an error is returned when the the MC firmware is started (see the snippet below), you can investigate its cause by displaying the log buffer in the U-Boot (assuming there is no console to print the MC output log).

```

fsl-mc: Booting Management Complex ... WARNING: Firmware returned an error (GSR: 0x19) fsl-mc: Management Complex booted (version: 10.29.0, boot status: 0x19)

```

The steps applied to print the log buffer contents in the U-Boot CLI are:

• Check that the current DPC has the following configuration:

```

[...]

mc_general

{

log

{

mode = "LOG_MODE_ON";

level = "LOG_LEVEL_WARNING";

};

[...]

```

To display the current DPC, execute the following sequence of commands:

```

=> fdt addr 0x20e00000

=> fdt print

```

• Determine the MC firmware base. At the U-Boot prompt, execute "md" for address 0x8340020 (this is MCFBA{L/H}):

The value at 0x08340024 is the MCFBAH address. In this case, it is 0x00000027. The value at 0x08340020 is the MCFBAL address. In this case, it is 0xe0000000. The MCFBA base address is built as 0x27e0000000.

Dump the log buffer structure at offset 0x01000000 from the MCFBA base address 0x27e1000000:

0x4d430100 is the magic number, 0x400000 is the log buffer offset, and 0x00300000 is the log buffer length.

• Dump the content of the log buffer. The output size can be increased by specifying the number of objects. In the following caption, the number of objects is 100:

```

=> md 0x27e1400000 100

```

#### 3.1.2 MACs physical offset

Table 1 lists the physical offsets for the MACs on the LX2. These offsets are useful when you read the PCS (or any register of the MAC ports) that are interrogated in the debug process.

Table 1. MAC base addresses

| MAC | Base address |

|-----|--------------|

| 1   | 0x8c07000    |

| 2   | 0x8c0b000    |

| 3   | 0x8c0f000    |

| 4   | 0x8c13000    |

| 5   | 0x8c17000    |

| 6   | 0x8c1b000    |

| 7   | 0x8c1f000    |

| 8   | 0x8c23000    |

| 9   | 0x8c27000    |

| 10  | 0x8c2b000    |

| 11  | 0x8c2f000    |

| 12  | 0x8c33000    |

| 13  | 0x8c37000    |

| 14  | 0x8c3b000    |

| 15  | 0x8c3f000    |

| 16  | 0x8c43000    |

| 17  | 0x8c47000    |

| 18  | 0x8c4b000    |

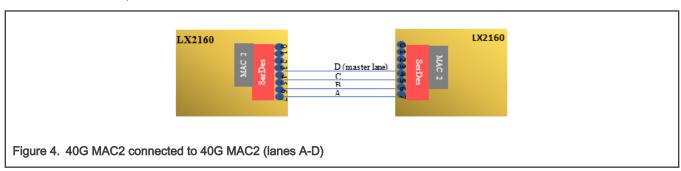

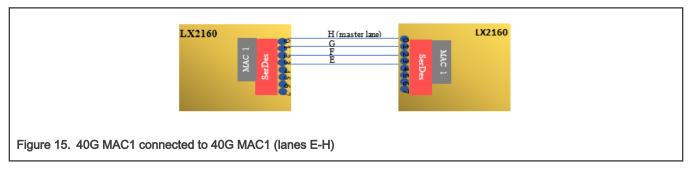

## 3.2 U-Boot use case with 40G MAC

In this setup (Figure 4), a 40G MAC (MAC2) is connected directly (SerDes to SerDes) to another 40G MAC (MAC 2) or to another device that has a 40G port.

Hypothesis:

Application Note 6 / 82

MAC2 uses lanes A-D on the SerDes1 module. The MAC is defined in the DPC file as:

```

[...]

board_info

{

ports

{

mac@2

{

link_type = "MAC_LINK_TYPE_FIXED";

};

}

```

The link type shows that there is no transceiver between the MAC and the peer. The connection is "TYPE\_FIXED".

If you want to send some packets from the left side to test the connectivity, launch the ping command from the CLI.

#### Result:

The outcome is that <u>no reply is received from the right side</u> either, because <u>there is no link</u> or something happens with the packets on the way between the two peers. The next caption contains the user commands and the result.

```

fsl-mc: Booting Management Complex ... SUCCESS

fsl-mc: Management Complex booted (version: 10.29.0, boot status: 0x1)

Hit any key to stop autoboot: 0

[...]

=> setenv ethact DPMAC2@xlaui4

=> ping 1.1.1.2

Using DPMAC2@xlaui4 device

Abort

ping failed; host 1.1.1.2 is not alive

```

The challenge here is to determine if a valid link is reported in the 40G PCS device status register.

The first step to exclude any SerDes problems (either configuration or hardware design integration issues - if the LX2 SoC is part of a custom design) is to execute a **sanity check**.

The next section describes the process.

#### 3.2.1 SerDes sanity check

This test checks the PCS link status when the SerDes is configured in the digital loopback.

In this mode, the link must always be up. Users can be skeptical, because they do not have access to the firmware source code and they consider the MC the root cause for a non-working setup. To rule out any potential problems that may be introduced by the MC firmware, the firmware must not be started in the validation procedure. This is equivalent to omitting the execution of the command that loads the MC binary file in the U-Boot environment:

```

#search through env variables and eliminate this command. Usually the mcinitcmd contains

it. Remove it from there and restart the board

#remove fsl_mc start mc 0x20a00000 0x20e00000;

```

To set a SerDes in the digital loopback, execute the following commands for lanes A-D (MAC2):

```

mw 0x1EA08A0 0x10000000

mw 0x1EA09A0 0x10000000

mw 0x1EA0AA0 0x10000000

mw 0x1EA0BA0 0x10000000

```

To read the link status bit, the MAC2 internal MDIO bus must be accessed. The pseudo code of this operation is described as "read <MAC> <PCS> <req>".

Network subsystem troubleshooting on DPAA2 devices (illustrated with LX2160), Rev. 0, 30 August 2021

Application Note 7 / 82

Here is a summary of the sanity check steps:

```

#in the U-Boot CLI modify the U-Boot env such that mc firmware is not started then reset the board

(after the reset, MC is not loaded)

#set lanes A-D in digital loopback

mw 0x1EA08A0 0x10000000

mw 0x1EA09A0 0x10000000

mw 0x1EA0AA0 0x10000000

mw 0x1EA0BA0 0x10000000

mw 0x1EA0BA0 0x10000000

#read the PCS status register from MAC2. see (*)

```

The next section describes an implementation variant to execute read/write operations on the internal MDIO bus.

#### 3.2.1.1 Internal MDIO command implementation

This command uses the skeleton of the standalone applications from the U-Boot tree. The U-Boot version used in this document is here.

The next snippet expands the **examples** folder inside the U-Boot tree and shows the **mdio** folder and its contents that were forked from the standalone application. Inside the **mdio** folder is the MDIO source that contains the implementation to access the internal MDIO bus for a given MAC.

```

examples/

- api

- crt0.S

— demo.c

├─ glue.c

- glue.h

libgenwrap.c

L Makefile

Makefile

- mdio

- libstubs.o

— Makefile

- mdio

- mdio.bin

- mdio.c

- mdio.o

- mdio.srec

- mdio.su

— ppc longjmp.S

- ppc_setjmp.S

- stubs.c

- stubs.o

L stubs.su

- standalone

- atmel_df pow2.c

— hello world

- hello world.bin

- hello world.c

- hello world.o

- hello world.srec

- hello world.su

- libstubs.o

— Makefile

nds32.1ds

— ppc_longjmp.S

ppc setjmp.S

```

```

- README.smc91111_eeprom

- sched.c

— smc91111 eeprom.c

- smc911x eeprom.c

— sparc.lds

```

The content of the MDIO source can be used as a reference implementation. The code below works for both Clause 45 and Clause 22 MDIO commands. Clause 45 is activated by default. This document presents use cases only with Clause 45.

```

diff --git a/examples/Makefile b/examples/Makefile

index d440bc5655..f0bcb03f42 100644

--- a/examples/Makefile

+++ b/examples/Makefile

@@ -6,6 +6,6 @@ ifdef FTRACE

subdir-ccflags-y += -finstrument-functions -DFTRACE

endif

-subdir-y += standalone

+subdir-y += standalone mdio

subdir-$(CONFIG API) += api

endif

diff --git a/examples/mdio/mdio.c b/examples/mdio/mdio.c

new file mode 100644

index 0000000000..10d1f18f40

--- /dev/null

+++ b/examples/mdio/mdio.c

@@ -0,0 +1,227 @@

+// SPDX-License-Identifier: GPL-2.0+

+/*

+ * (C) Copyright 2000

+ * Wolfgang Denk, DENX Software Engineering, wd@denx.de.

+#include <common.h>

+#include <exports.h>

+#include <stdlib.h>

+#include <stdio.h>

+#include <string.h>

+#include <asm/io.h>

+#include <linux/errno.h>

+#include <asm/arch/soc.h>

+#define MEMAC MDIO CFG 0x30

+#define MEMAC MDIO CTRL 0x34

+#define MEMAC MDIO DATA 0x38

+#define MEMAC MDIO ADDR 0x3c

+#define USAGE "Usage: go 0x80300000 <read|write> <mac offset> <mmd> <reg> [data]\n"

+struct mdio info {

u32 *mdio cfg;

u32 *mdio ctrl;

u32 *mdio addr;

u32 *mdio data;

u32 phy;

u32 ext phy;

u32 reg;

u32 mac addr;

```

```

u32 data;

+};

+static void mdio write(struct mdio info *bus, int cl45)

+ {

+

u32 temp;

bus->phy = (bus->ext phy << 5) | bus->phy;

temp = in le32(bus->mdio cfg);

if (cl45) {

temp = (temp & 0xFF80) | 0x1C | 0x40;

} else {

temp = (temp & 0xFF80) | 0x1C;

out le32 (bus->mdio cfg, temp);

temp = in le32(bus->mdio cfg);

temp = temp & 1;

while (temp) {

printf("mdio cfg bsy set\n");

temp = in le32(bus->mdio cfg);

temp = temp & 1;

udelay(500);

if (c145) {

out le32(bus->mdio ctrl, bus->phy);

out le32(bus->mdio addr, bus->reg);

} else {

out le32(bus->mdio ctrl, bus->reg);

temp = in le32(bus->mdio cfg);

temp = temp & 1;

while (temp) {

printf("mdio cfg bsy set\n");

temp = in le32(bus->mdio cfg);

temp = temp & 1;

+

udelay(500);

+

out le32(bus->mdio data, bus->data);

temp = in le32(bus->mdio data);

temp = temp | 0x80000000;

while (temp) {

printf("mdio data bsy set\n");

temp = in le32(bus->mdio data);

temp = temp & 0x80000000;

udelay(500);

+

}

return;

+}

+static void mdio read(struct mdio info *bus, int cl45)

+ {

u32 temp;

```

```

bus->phy = (bus->ext phy << 5) | bus->phy;

temp = in le32(bus->mdio cfg);

if (cl45) {

temp = (temp \& 0xFF80) | 0x1C | 0x40;

} else {

temp = (temp \& 0xFF80) | 0x1C;

out le32(bus->mdio cfg, temp);

temp = in le32(bus->mdio cfg);

temp = temp & 1;

while (temp) {

printf("mdio cfg bsy set\n");

temp = in le32(bus->mdio cfg);

temp = temp & 1;

udelay(500);

}

if (cl45) {

out le32(bus->mdio ctrl, bus->phy);

out le32(bus->mdio addr, bus->reg);

temp = in le32(bus->mdio cfg);

temp = temp & 1;

while (temp) {

printf("mdio cfg bsy set\n");

temp = in_le32(bus->mdio_cfg);

temp = temp & 1;

udelay(500);

}

if (cl45)

temp = bus->phy | 0x8000;

else

temp = bus->reg | 0x8000;

if (cl45)

out le32(bus->mdio ctrl, temp);

else {

out le32(bus->mdio ctrl, temp);

temp = in le32(bus->mdio_cfg);

temp = temp & 1;

while (temp) {

printf("mdio cfg bsy set\n");

temp = in le32(bus->mdio cfg);

temp = temp & 1;

udelay(500);

}

temp = in le32(bus->mdio data);

temp = temp | 0x80000000;

while (temp) {

printf("mdio data bsy set\n");

temp = in le32(bus->mdio data);

temp = temp & 0x80000000;

udelay(500);

```

```

temp = in le32(bus->mdio data);

printf ("\n\noutput data: 0x%08x\n", temp);

+

return;

+}

+int mdio (int argc, char * const argv[])

+ {

int i;

struct mdio info internal mdio = {0};

u32 temp;

static const char *mapping[] = {

[0] = "",

[1] = "operation",

[2] = "mac offset",

[3] = "dev addr",

[4] = "reg addr",

[5] = "data",

[6] = ""

};

/* Print the ABI version */

app startup(argv);

printf ("Example expects ABI version %d\n", XF VERSION);

printf ("Actual U-Boot ABI version %d\n", (int)get version());

printf ("Internal MDIO read / write \n");

printf ("argc = %d\n", argc);

for (i = 1; i < argc; ++i) {

printf ("%s = \"%s\"\n",

mapping[i],

argv[i] ? argv[i] : "<NULL>");

internal mdio.mac addr = (u32)strtoul(argv[2], NULL, 0);

internal_mdio.phy = (u32)strtoul(argv[3], NULL, 0);

internal mdio.reg = (u32)strtoul(argv[4], NULL, 0);

internal mdio.mdio cfg = (u32 *) (internal mdio.mac addr +

MEMAC MDIO CFG);

internal mdio.mdio ctrl = (u32 *) (internal mdio.mac addr +

MEMAC MDIO CTRL);

internal mdio.mdio addr = (u32 *)(internal mdio.mac addr +

MEMAC MDIO ADDR);

internal mdio.mdio data = (u32 *)(internal_mdio.mac_addr +

MEMAC MDIO DATA);

if (!strcmp(argv[1], "read")) {

int cl = 0;

if (argc == 5)

cl = 1;

if ((argc != 5) && (argc != 6))

printf(USAGE);

else

mdio read(&internal mdio, cl);

if (!strcmp(argv[1], "write")) {

int cl = 0;

```

```

+

internal_mdio.data = (u32)strtoul(argv[5], NULL, 0);

+

if (argc == 6)

cl = 1;

+

if ((argc != 6) && (argc != 7))

printf(USAGE);

+ else

+ mdio_write(&internal_mdio, cl);

+ }

+

printf("\n\n");

+ return (0);

+}

```

The MDIO standalone application is built together with the U-Boot and the resulted image (**mdio.bin**) is loaded into the U-Boot and executed. The detailed steps for building the U-Boot using a standalone toolchain are here.

NOTE

There is no need to change the U-Boot on the target device when building this application. Compile the U-Boot as usual and transfer the resulted MDIO binary to the target boards.

After the MDIO standalone application is compiled, determine the entry point address in the DDR memory where the binary is loaded and launched from the U-Boot CLI:

```

aarch64-linux-gnu-readelf ./examples/mdio/mdio -a | grep -i entry

Entry point address: 0x80300000

```

In this case, the address is 0x80300000.

Coming back to the sanity check process, the last step (see SerDes Sanity check) is to read the PCS status register:

```

# Display the env variable that loads the mdio binary

printenv elf load

elf load=dcache off; tftp 0x80300000 b37577/mdio.bin; dcache on;

run elf load

#(*) Read the PCS status register for MAC2 (see Table 1)

go 0x80300000 read 0x8c0b000 3 1

## Starting application at 0x80300000 ...

Example expects ABI version 9

Actual U-Boot ABI version 9

Internal MDIO read / write

argc = 5

operation = "read"

mac offset = "0x8c0b000"

dev addr = "3"

reg addr = "1"

mdio cfg bsy set

mdio data bsy set

output data: 0x00000004

## Application terminated, rc = 0x0

```

Application Note 13 / 82

The **"go 0x80300000 read 0x8c0b000 3 1" -** command launches the MDIO binary that is transferred at address 0x80300000. Its input arguments are:

- · Operation type: read/write, read in the above case

- MAC base address, 0x8c0b000 in the current case

- · MMD device address, PCS in this case offset 3

- Register address in the MMD space, in this example Status register address 1

NOTE

Run the above command multiple times to avoid latched data.

#### 3.2.1.2 SerDes sanity check result interpretation

The **output data** row from the read operation shows that the **Receive Link Status (bit 2 in Status Register)** is set (value of 0x00000004 - see the previous snippet). It means that there is a valid link in the PCS in the digital loopback mode, without running the MC firmware. This excludes a configuration issue on the SerDes.

If the **Receive Link Status bit** is not set, this points either to a configuration issue (RCW for example) or a problem in the design (decoupling caps, AVDD out of spec, and so on).

The next phases involve sending traffic from the LX2 to the peer from the right side, while different loopback modes are set (Figure 3 Loopback modes for 40G MAC). The idea is to incrementally verify that the traffic can be sent and received by the DPAA2 hardware without a problem.

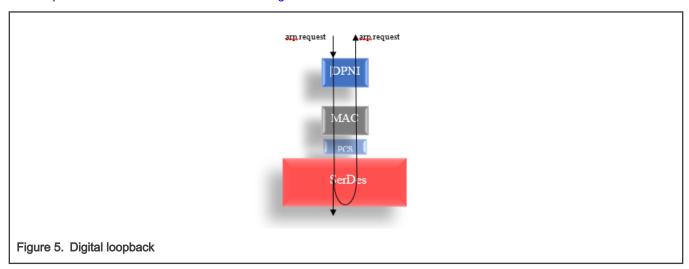

#### 3.2.2 Digital loopback

This case may seem redundant, because digital loopback was described in the previous section. The approach described here uses packets to verify both transmit and receive paths. Packets are gated in the serializer on the Rx side and looped from Tx to Rx.

The purpose of this test is to validate that the traffic (for example, ARP requests) can be successfully sent and received by the DPNI interface.

The simplified view of the traffic flow is shown in Figure 5.

The previous section shows that there is always a valid link present in the digital loopback.

The goal in this situation is to validate that the transmitted packets are looped and received back.

To eliminate any possible configuration problems related to link propagation between DPMAC and DPNI, some changes are applied in the U-Boot code and in the DPC file.

Application Note 14 / 82

NOTE

The modifications from the U-Boot are valid also for the PSC loopback (see PCS loopback).

#### 3.2.2.1 U-Boot changes

The objective of these changes is to report that the link is always up when a PHY is configured in the dpaa2 Ethernet driver probing sequence. For the PHY-less setup, these updates have no effect.

```

diff --git a/drivers/net/ldpaa eth/ldpaa eth.c b/drivers/net/ldpaa eth/ldpaa eth.c

index a3b9c152b2..1612827db2 100644

--- a/drivers/net/ldpaa eth/ldpaa eth.c

+++ b/drivers/net/ldpaa eth/ldpaa eth.c

@@ -17,7 +17,7 @@

#include <fsl-mc/ldpaa wriop.h>

#include "ldpaa eth.h"

+#define DEBUG

#ifdef CONFIG PHYLIB

static int init phy(struct eth device *dev)

diff --git a/drivers/net/phy/aquantia.c b/drivers/net/phy/aquantia.c

index 8ece926dd3..a149501119 100644

--- a/drivers/net/phy/aquantia.c

+++ b/drivers/net/phy/aquantia.c

@@ -554,6 +554,10 @@ int aquantia_startup(struct phy_device *phydev)

int i = 0;

phydev->duplex = DUPLEX FULL;

phydev->link = 1;

return 0;

/* if the AN is still in progress, wait till timeout. */

if (!aquantia link is up(phydev)) {

diff --git a/drivers/net/phy/phy.c b/drivers/net/phy/phy.c

index 33bce26e7f..3b32d7f234 100644

--- a/drivers/net/phy/phy.c

+++ b/drivers/net/phy/phy.c

@@ -222,6 +222,8 @@ int genphy update link(struct phy device *phydev)

{

unsigned int mii reg;

phydev->link = 1;

return 0;

* Wait if the link is up, and autonegotiation is in progress

* (ie - we're capable and it's not done)

```

The first update enables debug prints in the DPAA2 driver and the other two change the generic PHY driver and the AQR driver (AQR PHY is present on the LX2 RDB) behavior such that a linkup is always reported. If the link down event is reported by those functions, then the U-Boot init sequence for the DPAA2 Ethernet interfaces always fails when a ping command is launched.

NOTE

The U-Boot version used in the current document is here.

#### 3.2.2.2 DPC changes

```

[...]

board info {

ports {

```

Network subsystem troubleshooting on DPAA2 devices (illustrated with LX2160), Rev. 0, 30 August 2021

**Application Note**

The debug\_link\_check is always on, if it is not specified in the DPC. It has no effect if it is used on a MAC other than TYPE\_FIXED. This option must be used in a debug scenario where you want to put the MAC or PCS into the loopback for testing purposes. If there is a problem at the peer or SERDES level, a "link down" event propagates to the DPNI. In this situation, the Rx/Tx queues are disabled by the software layer (Linux DPAA2 driver or U-Boot) and no traffic can be sent/received. When this variable is set to "off", the link is always reported as up, even if it is not. Traffic can be sent/received by the WRIOP ports, making the PCS/MAC loopback a valid setup. This way you can validate that packets can be received/sent at the PCS/MAC level.

#### 3.2.2.3 Compiling U-Boot and DPC

After the U-Boot and DPC changes are applied, generate the firmware image and the DPC binary blob and write them to the target board. This document does not detail any build steps. They can be taken from here or from the *Layerscape Software Development Kit User Guide*.

There is an alternative to modify the DPC without deploying it into the flash on the running target.

This operation must be executed before starting the MC firmware. It saves the effort for compiling the DPC, deploying it, and flashing it to the board. This method can be used for any possible change that may be applied on the DPC.

```

#Do not start the MC firmware.(remove "fsl_mc start mc 0x20a00000 0x20e00000" from env and reboot the target, if the MC was already started)

#Assuming that the DPC is at address 0x20e00000 in flash (mapped to DDR), move the DPC to #a new DDR address (to be able to dynamically change it)

fdt addr 0x20e00000

fdt move 0x20e00000 0x85000000 0x5000

#Add the debug_link_check option

fdt addr 0x85000000

fdt rm /board_info/ports/mac@2

fdt mknode /board_info/ports mac@2

fdt set /board_info/ports/mac@2 link_type "MAC_LINK_TYPE_FIXED";

fdt set /board_info/ports/mac@2 debug_link_check "off";

#start the MC using the DPC from the new DDR address

fsl_mc start mc 0x20a00000 0x85000000;

```

#### 3.2.2.4 Digital loopback verification steps

The stages of running traffic in the digital loopback mode are as follows:

```

#after the firmware and DPC have been deployed on the target, reboot. For dynamically changing the

DPC without rebooting and flashing it, see previous section.

#Note MC firmware must be started in order to be able to use the interfaces

#A log as below should be seen:

fsl-mc: Booting Management Complex ... SUCCESS

fsl-mc: Management Complex booted (version: 10.29.0, boot status: 0x1)

Hit any key to stop autoboot: 0

#set lanes A-D in digital loopback

mw 0x1EA08A0 0x10000000

mw 0x1EA09A0 0x10000000

mw 0x1EA08A0 0x10000000

mw 0x1EA0BA0 0x10000000

#set ethact to be MAC2

```

```

setenv ethact DPMAC2@xlaui4

#run the ping command

=> ping 1.1.1.2

ldpaa dpmac bind, DPMAC Type= dpmac

ldpaa dpmac bind, DPMAC ID= 2

ldpaa dpmac bind, DPMAC State= 0

ldpaa dpmac bind, DPNI Type= dpni

ldpaa dpmac bind, DPNI ID= 0

ldpaa_dpmac_bind, DPNI State= 0

DPMAC link status: 1 - up

DPNI link status: 1 - up

Using DPMAC2@xlaui4 device

```

When the ping command is launched, do not expect to see an echo response. The purpose of this test is to receive the packets back, because the SerDes is in a digital loopback. The command is let to run for a couple of seconds. Then it is interrupted by pressing CTRL + C. The following output or a similar one (DPNI counters can differ but must not be 0) should be displayed in the console:

```

DPNI counters ..

DPNI CNT ING ALL FRAMES= 3

DPNI CNT ING ALL BYTES= 180

DPNI CNT ING MCAST FRAMES= 0

DPNI CNT ING MCAST BYTES= 0

DPNI CNT ING BCAST FRAMES= 3

DPNI CNT ING BCAST BYTES= 180

DPNI CNT EGR ALL FRAMES= 3

DPNI CNT EGR ALL BYTES= 126

DPNI CNT EGR MCAST FRAMES= 0

DPNI CNT EGR MCAST BYTES= 0

DPNI CNT EGR BCAST FRAMES= 3

DPNI CNT EGR BCAST BYTES= 126

DPNI CNT ING FILTERED FRAMES= 0

DPNI CNT ING DISCARDED FRAMES= 0

DPNI CNT ING NOBUFFER DISCARDS= 0

DPNI CNT EGR DISCARDED FRAMES= 0

DPNI_CNT_EGR_CNF_FRAMES= 0

DPMAC counters ..

DPMAC CNT ING BYTE=15

DPMAC_CNT_ING_FRAME DISCARD=11

DPMAC CNT ING ALIGN ERR =11

DPMAC_CNT_ING_BYTE=15

DPMAC CNT ING ERR FRAME=23

DPMAC CNT EGR BYTE =23

DPMAC CNT EGR ERR FRAME =27

Abort.

ping failed; host 1.1.1.2 is not alive

```

#### 3.2.2.5 Digital loopback result interpretation

The DPNI\_CNT\_ING\_ALL\_FRAMES and DPNI\_CNT\_EGR\_ALL\_FRAMES are equal to 3.

It means that 3 ARP requests were sent and received by the WRIOP port (DPNI).

The sent packets are arp and not echo requests, because before sending the echo request, the destination must be identified.

In parallel, it can be noticed that the PCS has a link due to the digital loopback configuration:

```

# Load the MDIO binary

go 0x80300000 read 0x8c0b000 3 1

## Starting application at 0x80300000 ...

Example expects ABI version 9

Actual U-Boot ABI version 9

Internal MDIO read / write

argc = 5

operation = "read"

mac offset = "0x8c0b000"

dev addr = "3"

reg addr = "1"

mdio_cfg bsy set

mdio_data bsy set

output data: 0x00000004

## Application terminated, rc = 0x0

```

NOTE

Run the above command multiple times to avoid latched data.

This result excludes any issues in both DPMAC and DPNI.

In case of a negative result (if no packets were received at the DPNI level), a possible issue is at the PCS (though very unlikely). The next stage checks this block by putting it into loopback.

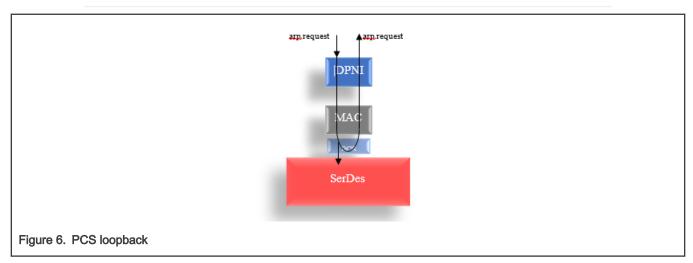

#### 3.2.3 PCS loopback

In a PCS loopback, data is transmitted normally. On the Rx side, it is discarded at the PMA level (from a SerDes perspective). The ARP requests sent from the U-Boot are looped inside a PCS and received in the WRIOP port (DPNI).

NOTE

It is not mandatory to have a link in the PCS when testing this configuration. If there is a link problem for whatever reason (at the peer side for example) or packets cannot be observed going in or out from LX2, a PCS loopback is a way to ensure that packets can be received without any issues at the DPNI/DPMAC level. From a clock perspective, there is no problem to use the PCS loop, because even if the peer is in a wrong state (it does not have a valid clock), the clock at the PCS (when in loopback) is recovered from the internal PLL.

Reading the PCS status register can yield 0x4 (link) or 0x0 (no link) and in both cases, the loopback should work correctly:

```

#load the MDIO binary

go 0x80300000 read 0x8c0b000 3 1

## Starting application at 0x80300000 ...

Example expects ABI version 9

Actual U-Boot ABI version 9

Internal MDIO read / write

argc = 5

operation = "read"

mac offset = "0x8c0b000"

dev addr = "3"

reg addr = "1"

mdio cfg bsy set

mdio data bsy set

#In this case there is no link

output data: 0x00000000

## Application terminated, rc = 0x0

```

NOTE Run the above command multiple times to avoid latched data.

#### 3.2.3.1 PCS loopback verification steps

The stages for running with traffic in PCS loopback are listed below. One observation is that before setting the PCS control register loopback bit (bit 14), its contents must be read then set the loopback bit.

The changes applied in U-Boot and DPC from the previous section (Digital loopback) must be used here as well.

```

#The same images should be used for this case

#Note MC firmware must be started in order to be able to use the interfaces

#A log as below should be seen:

fsl-mc: Booting Management Complex ... SUCCESS

fsl-mc: Management Complex booted (version: 10.29.0, boot status: 0x1)

Hit any key to stop autoboot: 0

#Display the env variable that loads the mdio binary

printenv elf load

elf load=dcache off; tftp 0x80300000 b37577/mdio.bin; dcache on;

run elf load

#set the PCS in loopback mode. First read the content of the control register

#read the PCS control register

go 0x80300000 read 0x8c0b000 3 0

## Starting application at 0x80300000 ...

Example expects ABI version 9

Actual U-Boot ABI version 9

Internal MDIO read / write

argc = 5

operation = "read"

mac offset = "0x8c0b000"

```

```

dev addr = "3"

reg addr = "0"

mdio cfg bsy set

mdio data bsy set

output data: 0x0000204c

#set the loopback bit

=> go 0x80300000 write 0x8c0b000 3 0 0x604c

## Starting application at 0x80300000 ...

Example expects ABI version 9

Actual U-Boot ABI version 9

Internal MDIO read / write

argc = 6

operation = "write"

mac offset = "0x8c0b000"

dev addr = "3"

reg addr = "0"

data = "0x604c"

mdio cfg bsy set

mdio data bsy set

## Application terminated, rc = 0x0

#set ethact to be MAC2

setenv ethact DPMAC2@xlaui4

#run the ping command

=> ping 1.1.1.2

ldpaa dpmac bind, DPMAC Type= dpmac

ldpaa_dpmac_bind, DPMAC ID= 2

ldpaa dpmac bind, DPMAC State= 0

ldpaa dpmac bind, DPNI Type= dpni

ldpaa dpmac bind, DPNI ID= 0

ldpaa dpmac bind, DPNI State= 0

DPMAC link status: 1 - up

DPNI link status: 1 - up

Using DPMAC2@xlaui4 device

```

When the ping command is launched, do not expect to see an echo response. The purpose of this test is to receive the packets back, because the PCS is in a loopback. The command is let to run for a couple of seconds. Then it is interrupted by pressing CTRL + C. The next output or a similar one (DPNI counters can differ but must not be 0) should be displayed in the console:

```

DPNI_CNT_ING_ALL_FRAMES= 2

DPNI_CNT_ING_ALL_BYTES= 120

DPNI_CNT_ING_MCAST_FRAMES= 0

DPNI_CNT_ING_MCAST_BYTES= 0

DPNI_CNT_ING_BCAST_FRAMES= 2

DPNI_CNT_ING_BCAST_BYTES= 120

DPNI_CNT_ING_BCAST_BYTES= 120

DPNI_CNT_EGR_ALL_FRAMES= 2

DPNI_CNT_EGR_ALL_BYTES= 84

DPNI_CNT_EGR_MCAST_FRAMES= 0

DPNI_CNT_EGR_MCAST_BYTES= 0

DPNI_CNT_EGR_MCAST_BYTES= 0

```

Application Note 20 / 82

```

DPNI CNT EGR BCAST BYTES= 84

DPNI CNT ING FILTERED FRAMES= 0

DPNI CNT ING DISCARDED FRAMES= 0

DPNI CNT ING NOBUFFER DISCARDS= 0

DPNI_CNT_EGR_DISCARDED FRAMES= 0

DPNI CNT EGR CNF FRAMES= 0

```

#### 3.2.3.2 PCS loopback result interpretation

#### DPNI\_CNT\_ING\_ALL\_FRAMES and DPNI\_CNT\_EGR\_ALL\_FRAMES equal to 2.

It means that 2 ARP requests are sent and received back by the WRIOP port (DPNI).

The result excludes any issue in both DPMAC and DPNI.

In case of a negative result (if no packets were received at the DPNI level), a possible problem is at the MAC level. The MAC loopback cannot be investigated in the U-Boot (see Interface loopback modes). This does not exclude a PCS issue, although this would be a very unlikely situation.

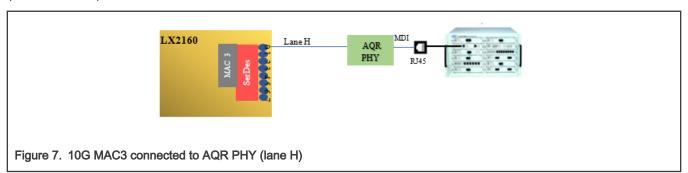

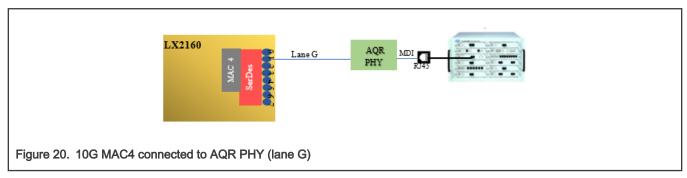

#### 3.3 U-Boot use case with 10G MAC

In this setup (Figure 7), a 10G MAC (MAC3) is connected to an AQR PHY that is further connected to a traffic generator device (or a workstation).

#### Hypothesis:

MAC3 uses Lane H on the SerDes1 module to connect to the AQR PHY (LX2 RDB). The MAC is defined in the DPC file as follows:

```

[...]

board info {

ports {

mac@3 {

link type = "MAC LINK TYPE PHY";

enet_if="USXGMII";

};

[...]

```

The link type shows that the MAC is connected to a PHY. The connection is called "TYPE\_PHY".

If you want to send packets from the left side to test the connectivity, launch the ping command from the CLI.

#### Result:

The outcome is that no reply is received from the right side (or no packets are captured by the Traffic Generator). It is either because there is no link or because something happens with the packets on the way between the two peers. The following code snippet contains the user commands and the result.

```

fsl-mc: Booting Management Complex ... SUCCESS

fsl-mc: Management Complex booted (version: 10.29.0, boot status: 0x1)

Hit any key to stop autoboot: 0

```

```

[...]

=> setenv ethact DPMAC3@xgmii

=> ping 1.1.1.2

Using DPMAC3@xgmii device

ping failed; host 1.1.1.2 is not alive

```

The only differences are that there is only one lane for MAC3 (lane H, base address 0x1EA0FA0) and its base address (0x8c0f000) is different from MAC2. For this use case, the debug steps listed in U-Boot use case with 40G MAC can be applied:

- · Digital loopback sanity check

- · Digital loopback with traffic

- · PCS loopback with traffic

This section covers only the PHY loopbacks.

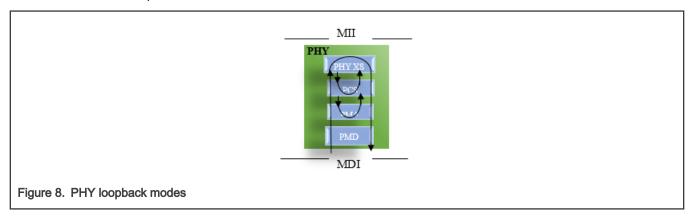

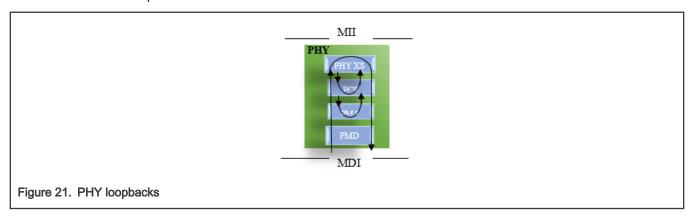

#### 3.3.1 PHY loopbacks

There are three types of loopbacks covered:

- PCS loopback the data is looped in the PCS and received up at the DPNI.

- PMA loopback the data is looped in the PMA and received at the DPNI.

- PHY XS loopback network loopback. The data sent from the peer is looped in the PHY XS and received by the peer. It is useful to validate the peer.

NOTE

When testing the first two modes, there is no need to have a valid link with the right peer (the Traffic Generator).

This document does not cover the technical details about these loopbacks. See the PHY data sheet for more information.

The loopback is configured using the U-Boot standard MDIO command. The PHY uses Clause 45 commands. It means that besides the PHY address and the register offset, the MMD device type must be provided as well (PCS, PMA, or PHY XS).

#### 3.3.1.1 PHY PCS loopback

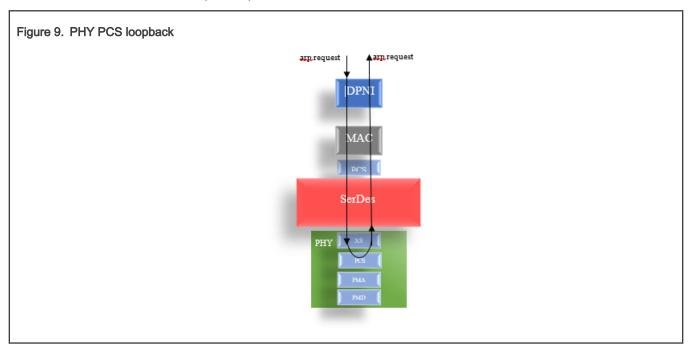

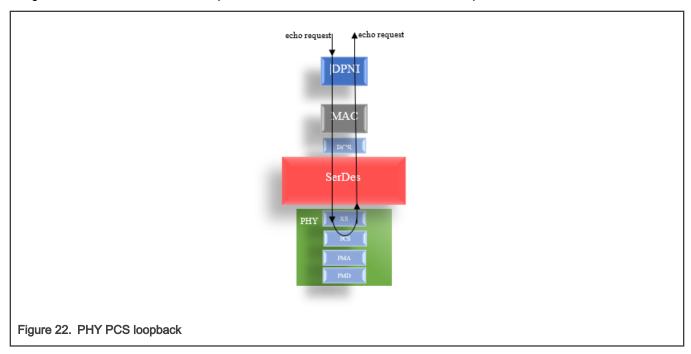

In this mode, when a ping command is executed, the ARP packets are generated from the U-Boot, sent down to the PHY (Figure 9), looped back in the PCS, and they reach back to the WRIOP port. All the packets are gated at the PCS level if no other option is set. It means that no data shows up at the peer side.

#### 3.3.1.1.1 PHY PCS loopback verification steps

Keep the same changed U-Boot image from U-Boot use case with 40G MAC. The DPC file can be restored to its initial content, because the debug\_link\_check option has no effect when the MAC is defined as TYPE\_PHY in the DPC (see DPC changes).

The steps for running this stage are:

```

#The same images should be used for this case

#Note MC firmware must be started in order to be able to use the interfaces

#A log as below should be seen:

fsl-mc: Booting Management Complex ... SUCCESS

fsl-mc: Management Complex booted (version: 10.29.0, boot status: 0x1)

Hit any key to stop autoboot: 0

[...]

#set ethact to be MAC3

=> setenv ethact DPMAC3@xgmii

#list the PHYs and select the PHY that corresponds to MAC3

mdio list

FSL MDIO0:

0 - Cortina CS4223 <--> DPMAC2@xlaui4

1 - AR8035 <--> DPMAC17@rgmii-id

2 - AR8035 <--> DPMAC18@rgmii-id

4 - Aquantia AQR107 <--> DPMAC3@xgmii

5 - Aquantia AQR107 <--> DPMAC4@xgmii

```

```

FSL MDIO1:

0 - Inphi in112525 S03P <--> DPMAC6@25g-aui

#display mdio options to see the arguments of the command

=> mdio

mdio - MDIO utility commands

Usage:

mdio list

- List MDIO buses

mdio read <phydev> [<devad>.]<reg> - read PHY's register at <devad>.<reg>

mdio write <phydev> [<devad>.]<reg> <data> - write PHY's register at <devad>.<reg>

mdio rx <phydev> [<devad>.]<reg> - read PHY's extended register at <devad>.<reg>

mdio wx <phydev> [<devad>.]<reg> <data> - write PHY's extended register at <devad>.<reg>

<phydev> may be:

<bushame> <addr>

<addr>

<eth name>

<addr> <devad>, and <reg> may be ranges, e.g. 1-5.4-0x1f.

#set PHY 4 in PCS loopback - set bit 14 in PCS control register (offset 0)

#first read then set bit 14 to 1

mdio read 4 3.0

4 is not a known ethernet

Reading from bus FSL MDIO0

PHY at address 4:

3.0 - 0x2040

mdio write 4 3.0 0x6040

#run the ping command

=> ping 1.1.1.2

ldpaa dpmac bind, DPMAC Type= dpmac

ldpaa dpmac bind, DPMAC ID= 3

ldpaa dpmac bind, DPMAC State= 0

ldpaa dpmac bind, DPNI Type= dpni

ldpaa dpmac bind, DPNI ID= 0

ldpaa dpmac bind, DPNI State= 0

DPMAC link status: 1 - up

DPNI link status: 1 - up

Using DPMAC3@xgmii device

```

When the ping command is launched, do not expect to see an echo response. The purpose of this test is to receive the packets back, because the PHY PCS is in a loopback. The command runs for a couple of seconds and it is then interrupted by pressing CTRL + C. The following (or similar) output (the DPNI counters can differ but they must not be 0) should be displayed in the console:

```

DPNI counters ..

DPNI_CNT_ING_ALL_FRAMES= 2

DPNI_CNT_ING_ALL_BYTES= 120

DPNI_CNT_ING_MCAST_FRAMES= 0

DPNI_CNT_ING_MCAST_BYTES= 0

DPNI_CNT_ING_BCAST_FRAMES= 2

DPNI_CNT_ING_BCAST_BYTES= 120

DPNI_CNT_EGR_ALL_FRAMES= 2

DPNI_CNT_EGR_ALL_FRAMES= 2

DPNI_CNT_EGR_ALL_BYTES= 84

DPNI_CNT_EGR_MCAST_FRAMES= 0

```

Network subsystem troubleshooting on DPAA2 devices (illustrated with LX2160), Rev. 0, 30 August 2021

Application Note 24 / 82

```

DPNI CNT EGR MCAST BYTES= 0

DPNI CNT EGR BCAST FRAMES= 2

DPNI CNT EGR BCAST BYTES= 84

DPNI CNT ING FILTERED FRAMES= 0

DPNI CNT ING DISCARDED FRAMES= 0

DPNI CNT ING NOBUFFER DISCARDS= 0

DPNI CNT EGR DISCARDED FRAMES= 0

DPNI CNT EGR CNF FRAMES= 0

```

#### 3.3.1.1.2 PHY PCS loopback result interpretation

#### DPNI\_CNT\_ING\_ALL\_FRAMES and DPNI\_CNT\_EGR\_ALL\_FRAMES equal 2.

It means that two ARP requests were sent and received back by the WRIOP port (DPNI).

The result excludes any issue with the PHY or with the other layers from the LX2.

In case of a negative result (if no packets were received at the DPNI level), a possible issue is at the PHY level (if the tests for the other layers on the LX2 have passed). Consult the PHY data sheet. The test included here is for the AQR PHY. The U-Boot does have a driver for it (see the changes applied in U-Boot changes), which means that the PHY is configured when the DPAA2 MACs are probed (grepping for Idpaa eth netdev init in the U-Boot source reveals the init phy function) For a different PHY, check whether a driver is needed or the generic driver can apply the basic settings.

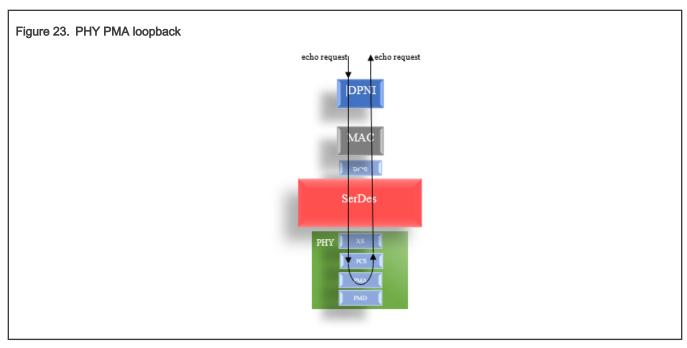

#### 3.3.1.2 PHY PMA loopback

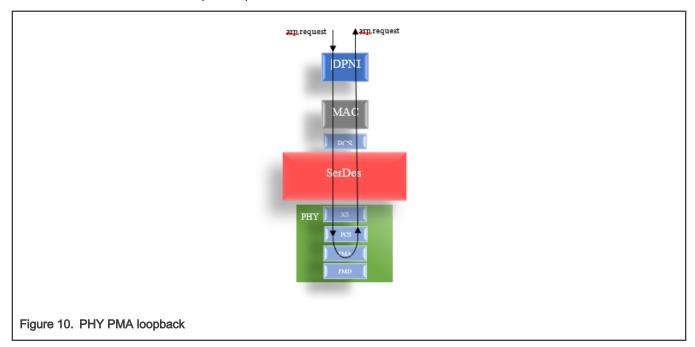

In this mode, when a ping command is executed, the ARP packets are generated from the U-Boot, sent to the PHY (Figure 10), looped back in the PMA, and they reach back to the WRIO port. All the packets are gated at the PMA level when no other option is set. It means that no data show up at the peer side.

#### 3.3.1.2.1 PHY PMA loopback verification steps

Keep the same changed U-Boot image from U-Boot use case with 40G MAC. The DPC file can be restored to its initial content, because the debug\_link\_check option has no effect when the MAC is defined as TYPE\_PHY in the DPC (see DPC changes).

The steps to run this stage are:

```

#The same images should be used for this case

#Note MC firmware must be started in order to be able to use the interfaces

#A log as below should be seen:

fsl-mc: Booting Management Complex ... SUCCESS

fsl-mc: Management Complex booted (version: 10.29.0, boot status: 0x1)

Hit any key to stop autoboot: 0

[...]

#set ethact to be MAC3

=> setenv ethact DPMAC3@xgmii

#list the PHYs and select the PHY that corresponds to MAC3

mdio list

FSL MDIO0:

0 - Cortina CS4223 <--> DPMAC2@xlaui4

1 - AR8035 <--> DPMAC17@rgmii-id

2 - AR8035 <--> DPMAC18@rgmii-id

4 - Aquantia AQR107 <--> DPMAC3@xgmii

5 - Aquantia AQR107 <--> DPMAC4@xgmii

FSL MDIO1:

0 - Inphi in112525 S03P <--> DPMAC6@25g-aui

#set PHY 4 in PMA loopback - set bit 0 in PMA(MMD offset 1) control register (offset 0)

#first read then set bit 0 to 1

mdio read 4 1.0

4 is not a known ethernet

Reading from bus FSL MDIO0

PHY at address 4:

- 0x2040

1.0

2.0

mdio write 4 1.0 0x2041

#run the ping command

=> ping 1.1.1.2

ldpaa dpmac bind, DPMAC Type= dpmac

ldpaa dpmac bind, DPMAC ID= 3

ldpaa_dpmac_bind, DPMAC State= 0

ldpaa dpmac bind, DPNI Type= dpni

ldpaa dpmac bind, DPNI ID= 0

ldpaa dpmac bind, DPNI State= 0

DPMAC link status: 1 - up

DPNI link status: 1 - up

Using DPMAC3@xgmii device

```

Network subsystem troubleshooting on DPAA2 devices (illustrated with LX2160), Rev. 0, 30 August 2021 **Application Note** 26 / 82 When the ping command is launched, do not expect to see an echo response. The purpose of this test is to receive the packets, because the PHY PMA is in a loopback. The command runs for a couple of seconds and it is then interrupted by presing CTRL + C. The following (or similar) output (the DPNI counters can differ, but they must not be 0) should show up in the console:

```

DPNI counters ..

DPNI CNT ING ALL FRAMES= 2

DPNI CNT ING ALL BYTES= 120

DPNI CNT ING MCAST FRAMES= 0

DPNI CNT ING MCAST BYTES= 0

DPNI CNT ING BCAST FRAMES= 2

DPNI_CNT_ING_BCAST_BYTES= 120

DPNI CNT EGR ALL FRAMES= 2

DPNI CNT EGR ALL BYTES= 84

DPNI CNT EGR MCAST FRAMES= 0

DPNI CNT EGR MCAST BYTES= 0

DPNI CNT EGR BCAST FRAMES= 2

DPNI CNT EGR BCAST BYTES= 84

DPNI CNT ING FILTERED FRAMES= 0

DPNI CNT ING DISCARDED FRAMES= 0

DPNI CNT ING NOBUFFER DISCARDS= 0

DPNI CNT EGR DISCARDED FRAMES= 0

DPNI CNT EGR CNF FRAMES= 0

```

#### 3.3.1.2.2 PHY PMA loopback result interpretation

#### DPNI\_CNT\_ING\_ALL\_FRAMES and DPNI\_CNT\_EGR\_ALL\_FRAMES equal 2.

It means that two ARP requests are sent and received by the WRIOP port (DPNI).

The result excludes any issues with the PHY or with the other layers from the LX2.

See also the comments in PHY PCS loopback result interpretation in case of a negative result.

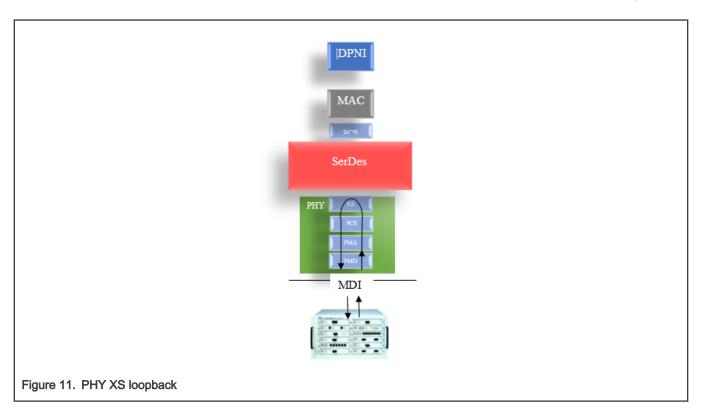

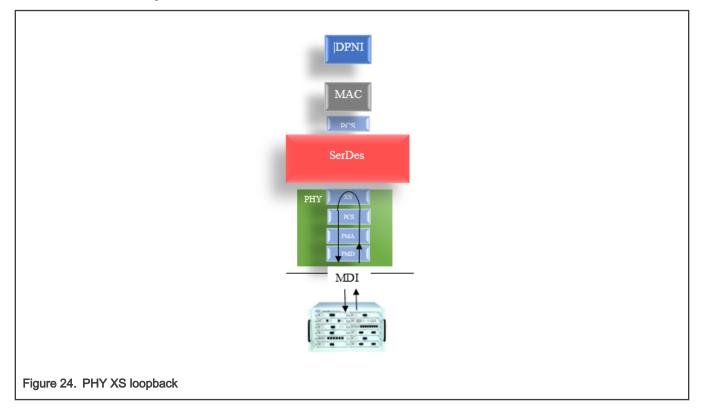

#### 3.3.1.3 PHY XS loopback

In this mode, the data is not sent from the LX2 side but from the Traffic Generator. The packets must be looped in the PHY XS layer and received in the Traffic Generator.

#### 3.3.1.3.1 PHY XS loopback verification steps

Keep the same changed U-Boot image from U-Boot use case with 40G MAC. The DPC file can be restored to its initial content, because the debug\_link\_check option has no effect when the MAC is defined as TYPE\_PHY in the DPC (see DPC changes).

The steps to run this stage are:

```

#The same images should be used for this case

#Note MC firmware must be started in order to be able to use the interfaces

#A log as below should be seen:

fsl-mc: Booting Management Complex ... SUCCESS

fsl-mc: Management Complex booted (version: 10.29.0, boot status: 0x1)

Hit any key to stop autoboot: 0

[...]

#list the PHYs and select the PHY that corresponds to MAC3

mdio list

FSL MDIO0:

0 - Cortina CS4223 <--> DPMAC2@xlaui4

1 - AR8035 <--> DPMAC17@rgmii-id

2 - AR8035 <--> DPMAC18@rgmii-id

4 - Aquantia AQR107 <--> DPMAC3@xgmii

5 - Aquantia AQR107 <--> DPMAC4@xgmii

FSL MDIO1:

0 - Inphi in112525 S03P <--> DPMAC6@25g-aui

#set PHY 4 in XS loopback - set bit 14 in XS(address 4) control register (offset 0)

#first read then set bit 14 to 1

```

```

mdio read 4 4.0

4 is not a known ethernet

Reading from bus FSL MDIO0

PHY at address 4:

4.0 - 0x2040

mdio write 4 4.0 0x6040

```

Inject a couple of packets from the Traffic Generator. All of them must be received. If no packets are received, check the PHY data sheet and the PHY configuration. In this case, it is unlikely that there is an issue at the Traffic Generator level.

# 4 Troubleshooting in Linux OS

#### 4.1 Introduction

Similarly to the U-Boot chapter, this section covers the cases in which the traffic is not received on an LX2 port as expected or the traffic does not reach the destination. The setup is similar to that shown in Figure 1.

Before delving into the use cases and considering the questions that are asked over time by multiple users regarding the DPAA2 architecture (for example; "What does a DPCON do?", "Do I need a DPCON to receive interrupts?", "What is the relation between DPCON, DPIO, and the GPPs?" "Is there any example of a poll mode driver without interrupts?", and so on), the following pages show an overview of the DPAA2 Linux OS architecture. It is not mandatory to read this part for the debugging scenarios. It is recommended when the investigations move to the driver code.

#### 4.2 DPAA2 Linux OS architecture overview

When choosing a programming mode for a DPAA2 network interface, there are two options:

• The poll mode is implemented in the U-Boot. In this case, the interrupts are not enabled. The U-Boot DPAA2 Ethernet driver polls continuously, as shown in the following snippet:

```

[...]

qbman swp pull(dflt dpio->sw portal , &pulldesc);

do {

dq = qbman_swp_dqrr_next(swp);

} while (get_timer(time_start) < timeo && !dq);</pre>

```

A command such as ping is executed until the timeout expires or frames are received on the Rx queue.

NOTE

In this mode, manage the polling event to avoid the consumption of CPU cycles for polling only.

The polling pertains to the U-Boot, where only one core is active and the interface becomes available when a command that uses one of the ports (for example, ping) is executed in the CLI. When the command finishes (for example, when some packets are received/sent), the interface is disabled and the core goes back to poll for a CLI input. The poll mode is implemented in the DPAA2 ETH driver from DPDK as well.

The interrupt mode is used in the Linux OS (together with the NAPI). This functionality is detailed in the following lines.

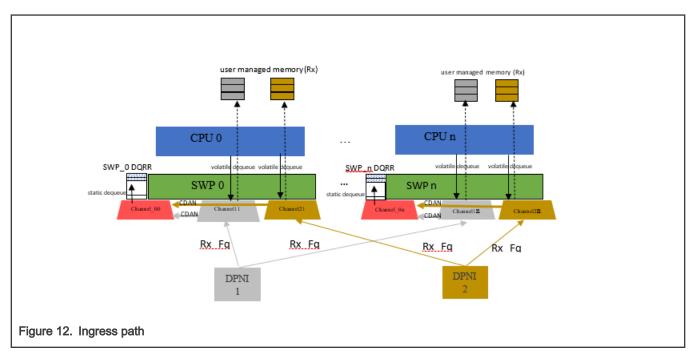

The ingress path with all its architectural components is shown in Figure 12.

Each DPNI has its own resources (the colors indicate which objects belong to DPNI). It has a number of channels and each channel affines to a software portal. It has a number of frame queues affined for each core. If multiple traffic classes are defined on the ingress side, then there are multiple frame queues per core. If there is one traffic class per DPNI, then there is one queue per core. The traffic classes are not represented in Figure 12 for simplicity reasons.

Each Rx queue belongs to WQ1 (work queue - a DPAA2 hardware resource) in each channel, affined to each core: for DPNI1, the Rx queue for CPU0 belongs to WQ1 in Channel11 and the Rx queue for CPUn belongs to WQ1 in Channel 1n.

The frames received on DPNI1 are enqueued to queues belonging to Channel11 through to Channel1n and they are dequeued by CPU0 [...] CPUn from the corresponding affined channel.

The following snippet from the DPAA2 ETH driver shows the connections between the channel, the WQ, and the frame queue:

NOTE

The Linux OS version used in this document is here.

A channel is equivalent to a DPCON object. In Figure 12, the DPNI1 has DCPCON1 to DPCONn ("n" DPCONs in total) and DPNI2 has the same number of DPCONs. The "n" represents the number of software portals (cores) assigned to a DPNI. It can be a maximum of 16 for the LX2.

There is a special DPCON per each software portal - DPCON0. DPCON0 is equivalent with Channel00 on CPU0 with Channel0n on CPUn and is shared by DPNI1 and DPNI2.

Application Note 30 / 82

Each DPNI channel is configured to deliver CDANs (Channel Data Availability Notifications) to DPCON0 (see Figure 12 for how the CDAN from each DPNI's private channel is delivered in the same DPCON0 on the same CPU. The DPCON0 is called the CDAN channel. The CDAN notification is delivered to the first WQ from the DPCON0 - WQ0 (the highest priority WQ).

These CDAN channels relay the CDANs into a software portal memory location called DQRR, where they are consumed and processed by the CPU.

The following snippet shows how the CDAN channels are configured for each online CPU:

```

for each online cpu(i)

[...]

/* Register DPCON notification with MC */

dpcon notif cfg.dpio id = nctx->dpio id;

dpcon_notif_cfg.priority = 0;

dpcon notif cfg.user ctx = nctx->qman64;

err = dpcon set notification(priv->mc io, 0,

channel->dpcon->mc handle,

&dpcon notif cfg);

[...]

```

Each private channel is configured to deliver CDANs:

```

[...]

channel = alloc channel(priv);

if (IS ERR OR NULL(channel)) {

err = PTR ERR OR ZERO(channel);

if (err != -EPROBE DEFER)

dev info(dev,

"No affine channel for cpu %d and above\n", i);

goto err alloc ch;

priv->channel[priv->num channels] = channel;

nctx = &channel->nctx;

nctx->is cdan = 1;

[...]

```

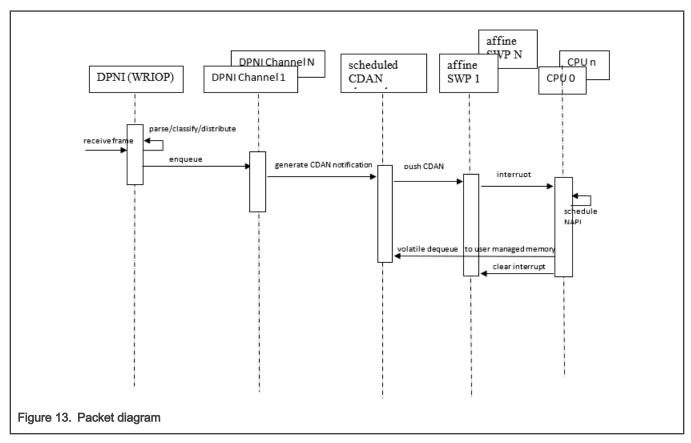

For a clearer picture of the ingress flow, Figure 13 describes how a packet is delivered to the CPU and placed in the user managed memory.

A frame that arrives in a DPNI and passes the MAC filters (in CTLU) is subject to an advanced exact-match filter (also in the CTLU). If a frame matches one of the exact match table entries, it is steered to one of the Frame Queue Destination IDs. Otherwise, the frame enters a hash distribution stage, which delivers the frame to one of the CPUs (still via DPNI's queues) according to its determined traffic class. The frame (if not malformed or in other way erroneous) is eventually enqueued to a FQ placed in one of the DPNI's private channels (DPCON1 to DPCONn) configured in the volatile dequeue mode.

Each DPNI's private channel is configured to deliver CDAN notifications into a CDAN channel.

Each CDAN channel is affined to a CPU, but the CDAN channels are shared across multiple DPNIs. There are as many CDAN channels as there are CPUs and it is the same with the DPNI's private channels.

Unlike the DPNI's private channels, the shared CDAN channels are configured in the scheduled dequeue mode. They push the newly received CDANs as soon as the scheduling logic dictates. Each CDAN channel has only one SWP to service, which makes it CPU-affined.

When receiving the CDAN, the SWP raises an interrupt to the GPP. The portal interrupt handler consumes the CDAN and identifies the DPNI that produced the notification:

```

irqreturn t dpaa2 io irq(struct dpaa2 io *obj)

{

const struct dpaa2 dq *dq;

int max = 0;

struct qbman swp *swp;

u32 status;

swp = obj->swp;

status = qbman swp interrupt read status(swp);

if (!status)

return IRQ_NONE;

[...]

dq = qbman swp dqrr next(swp);

while (dq) {

```

```

if (qbman result is SCN(dq)) {

struct dpaa2 io notification ctx *ctx;

u64 q64;

q64 = qbman result SCN ctx(dq);

ctx = (void *) (uintptr t) q64;

ctx->cb(ctx);

} else {

pr crit("fsl-mc-dpio: Unrecognised/ignored DQRR entry\n");

qbman_swp_dqrr_consume(swp, dq);

++max;

if (max > DPAA POLL MAX)

goto done;

dq = qbman_swp_dqrr next(swp);

}

```

#### NOTE

When a CDAN is placed on its WQ, the CDAN generation is disabled automatically in the channel which generated the CDAN. No more CDANs are issued from this channel until it is reenabled by software.

The interrupt handler calls the DPNI CDAN callback (ctx->cb(ctx)) that schedules a NAPI instance:

```

static void cdan cb(struct dpaa2 io notification ctx *ctx)

{

struct dpaa2 eth channel *ch;

ch = container of(ctx, struct dpaa2 eth channel, nctx);

/* Update NAPI statistics */

ch->stats.cdan++;

napi schedule irqoff(&ch->napi);

```

A volatile dequeue command from the NAPI instance is issued from the source channel of the CDAN into the DPNI's user-defined memory on a particular CPU:

```

do {

err = pull channel(ch);

if (unlikely(err))

break;

/* Refill pool if appropriate */

refill pool(priv, ch, priv->bpid);

store cleaned = consume frames(ch, &fq);

} while (store cleaned);

```

The CPU further consumes the frame:

```

static int consume frames(struct dpaa2 eth channel *ch,

struct dpaa2 eth fq **src)

{

fq->consume(priv, ch, fd, fq);

```

The CPU then sends it to the stack:

```

/* Main Rx frame processing routine */

static void dpaa2_eth_rx(struct dpaa2_eth_priv *priv,

struct dpaa2_eth_channel *ch,

const struct dpaa2 fd *fd,

```

This is a very short description of the ingress path.

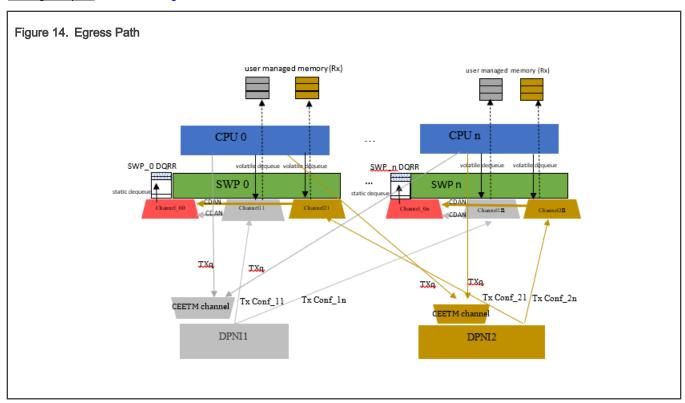

The egress path is shown in Figure 14.

Each DPNI has a private CEETM (Customer Edge Egress Traffic Management) channel with 16 class queues. The DPAA2 driver supports only 8 class queues and 1 CEETM channel. The number of Tx queues for each interface equals the number of Rx queues. Each inbound flow has a correspondent in the outbound direction.

The CPUs use the software portals to enqueue the frames in the Tx queues.

Each queue belongs to a traffic class (0..7), which gives the queue priority value, which is used when the final enqueue action is executed on the CPU.

The priority is determined as follows:

```

queue_mapping = skb_get_queue_mapping(skb);

if (net_dev->num_tc) {

prio = netdev_txq_to_tc(net_dev, queue_mapping);

```

The priority is used to select the corresponding Tx queue that belongs to the traffic class mapped to that priority. In the resulted queue, the CPU enqueues the data as follows:

Network subsystem troubleshooting on DPAA2 devices (illustrated with LX2160), Rev. 0, 30 August 2021

Application Note 34 / 82

```

[...]

```

The above enqueue callback expands to:

```

err = dpaa2 io service enqueue multiple fq(fq->channel->dpio,

fq->tx fqid[prio],

fd, num frames);

```

The corresponding class queue is identified according to the priority value (in hardware 0 is the highest, 7 is the lowest) that selected the destination queue inside the CEETM channel. It is based on an internal CEETM mapping table.

Depending on how the frames are scheduled and sent to the physical port, it is up to the class queue scheduler (in the CEETM) to decide which class gueue to pick from the 8 available. It decides according to their priorities. By default, the 8 class gueues have a strict priority from 0 to 7.

For more details about the CEETM, see the LX2 reference manual.

After a frame is transmitted, the buffer occupied by it must be freed either into the buffer pool (each interface has a private buffer pool to which the frame is copied by the WRIOP from the internal FIFO) or to the allocator (in Linux OS).

Freeing the packet to the buffer pool can be done using an external buffer deallocation mechanism. If this option is enabled, a DPNI automatically frees a buffer to its buffer pool when the frame is transferred from its external buffer to the internal FIFO. It can be used on the forwarding path.

Nearly all the traffic locally originated must be freed to the allocator. This is done using the Tx confirmation mechanism. This mechanism implies a dedicated queue (one queue per core) and the following requirements apply:

- The traffic is spread across all CPUs. Each flow (CPU) has its own Tx confirmation queue, so no CPU processes the Tx confirmation traffic from the other CPUs.

- Due to the affinity of flows to the CPUs on each egress flow, the Tx confirmed buffers should be freed by the same CPU that allocated them.

- The Tx confirmation queues have a higher priority than any ingress queues. The Tx confirmation queues are special Rx queues. They work in a way similar to the Rx queues. The code that set the Rx queue is similar to the code that sets the Tx confirmation queues. The only significant difference is the WQ priority. Each Tx confirmation queue belongs to WQ0. Each WQ0 is in Channel11 to Channel1n when it belongs to DPNI1 or Channel21 to Channel2n when it belongs to DPNI2, together with WQ1 used for the Rx gueues.

```

queue.destination.id = fq->channel->dpcon id;

queue.destination.type = DPNI DEST DPCON;

queue.destination.priority = 0;

queue.user context = (u64) (uintptr t) fq;

err = dpni set queue(priv->mc io, 0, priv->mc token,

DPNI QUEUE TX CONFIRM, 0, fq->flowid,

DPNI QUEUE OPT USER CTX | DPNI QUEUE OPT DEST,

&queue);

```

There is one error queue per DPNI configured in a similar way with the Tx confirmation and Rx queues. They belong to the same WQ1 as the Rx queues. By default, the error queue is disabled in the kernel configuration. In case of an error, the packets are discarded.

```

q.destination.id = fq->channel->dpcon id;

q.destination.type = DPNI DEST DPCON;

q.destination.priority = 1;

q.user context = (u64) fq;

err = dpni set queue (priv->mc io, 0, priv->mc token,

DPNI QUEUE RX ERR, 0, 0, q opt, &q);

```

Network subsystem troubleshooting on DPAA2 devices (illustrated with LX2160), Rev. 0, 30 August 2021 **Application Note** 35 / 82

NOTE

The error queue is not shown in the figure. It uses the same CDAN mechanism as the Rx and Tx confirmation queues.

Now that the Rx and Tx path were described, some considerations on the interrupts and DPAA2 objects follow.

The MC logical objects can interrupt the CPU(s) by executing Message Interrupts (MSI). The MSIs are generated by writing specific values to the dedicated addresses. The addresses are mapped to the SoC interrupt controller's MSI mechanism, although the MC should not be aware of the implementation details of the MSI mechanism. The allocation of an MSI address and the data to write to that address are the responsibility of the CPU device driver, because they are system resources. The MC simply writes the specified data to the given address (assuming that it falls into the SoC CCSR access window) whenever there is a need to generate the associated interrupt.

The interrupts handling API is similar among all MC logical objects. Each logical object may define one or more interrupts. Each interrupt (IRQ) is associated with a pair of MSI address and data. Every interrupt can have up to 32 causes and the interrupt model supports masking/unmasking each cause independently. Grouping the causes into an interrupt is defined by the object's API. The error causes are grouped separately from normal runtime events.

In the case of DPNI, whenever a link change event is transmitted by the lower layers, the associated IRQ handler is called. In the DPAA2 ETH driver, the events that may trigger the interrupt are highlighted in the following snippet:

```

static irqreturn t dpni irq0 handler thread(int irq num, void *arg)

{

u32 \text{ status} = \sim 0;

struct device *dev = (struct device *)arg;

struct fsl mc device *dpni dev = to fsl mc device(dev);

struct net device *net dev = dev get drvdata(dev);

err = dpni get irq status(dpni dev->mc io, 0, dpni dev->mc handle,

DPNI IRQ INDEX, &status);

if (unlikely(err)) {

netdev err(net dev, "Can't get irq status (err %d)\n", err);

return IRQ HANDLED;

if (status & DPNI IRQ EVENT LINK CHANGED)

link state update(netdev priv(net dev));

if (status & DPNI_IRQ_EVENT_ENDPOINT_CHANGED)

set mac addr(netdev priv(net dev));

return IRQ HANDLED;}

```

For the DPMAC, the events that can trigger an interrupt are in the following snippet:

```

static irqreturn t dpaa2 mac irq handler(int irq num, void *arg)

{

[...]

/* DPNI-initiated link configuration; 'ifconfig up' also calls this */

if (status & DPMAC IRQ EVENT LINK CFG REQ) {

if (cmp dpmac ver(priv, DPMAC LINK AUTONEG VER MAJOR,

DPMAC LINK AUTONEG VER MINOR) < 0)

err = dpmac_get_link_cfg(mc_dev->mc_io, 0,

mc dev->mc handle, &link cfg);

else

err = dpmac get link cfg v2 (mc dev->mc io, 0,

mc dev->mc handle,

&link cfg);

if (unlikely(err))

goto out;

configure link(priv, &link cfg);

if (status & DPMAC IRQ EVENT LINK DOWN REQ)

```

37 / 82

```

phy_stop(ndev->phydev);

if (status & DPMAC_IRQ_EVENT_LINK_UP_REQ)

phy_start(ndev->phydev);

```

The MC internal link manager periodically checks the connection state between objects (for example, in case of the DPNI, the connection state with a DPMAC, if the network interface is composed of a DPNI connected to a physical MAC) and when it receives an event (for example, the PHY lost the link on the line side or there is no link in the PCS for some reason), it propagates the state change to the objects and triggers an interrupt.

The sequence below describes the general flow of events from the point when the data value is written until the CPU receives the interrupt.

1. Data is written to the GIC ITS GITS\_TRANSLATER register.

There is only one ITS in the GIC-500. It means that all devices write to the same physical address to trigger interrupts. A non-spoofable "device id" is expressed as part of the transaction as well. In the case of DPAA2 devices/objects, all objects in the same container/DPRC share the same "device-id". For the Arm-based SoC, this is the same as the stream ID. The "data" value is an interrupt number.

- 2. The data and stream ID must pass through the SMMU unchanged.

- 3. The GIC ITS does a lookup of the "device id" in a device table to identify an Interrupt Translation Table (ITT)

- 4. The data value indexes into the ITT, identifying an interrupt table entry.

- 5. The table entry has a collection ID that identifies a collection table entry that points to the destination CPU. The table entry also identifies the physical LPI number.

- 6. With the destination CPU identified, the ITS writes to the level 0 redistributor for the destination CPU to trigger the physical LPI.

- 7. The interrupt occurs at the CPU.

- 8. The CPU reads GICC\_IAR, getting the physical LPI number.

# 4.3 Data Path Layout (DPL)

To enable the DPAA2 network interfaces on a running Linux OS, load the DPL file during boot time (in the boot loader, before booting the kernel image).

The DPL describes a set of objects that are created when the system (Linux OS) is initialized.

The following are some aspects related to the DPL:

- The DPL is found at flash offset = 0xd00000/SD Card offset = 0x6800.

- The DPL is similar to the DTS. However, it does not describe the hardware attributes, but the initial topology of logical objects that the MC firmware should create.

- The DPL can be compiled using the "dtc" tool. A blob similar to the DTB is generated.

- The DPL is applied after the MC boots (it is not executed automatically): fsl\_mc apply dpl <dpl\_addr>.

- When the DPL is applied, all the objects from the U-Boot (DPNI, DPMAC, and so on) are deleted and the network

interfaces are no longer available from the U-Boot. To use the interfaces in the boot loader again, reboot the board without

applying the DPL.

- · Some examples are at this link.

# 4.3.1 Booting Linux OS with a minimal DPL file

In troubleshooting contexts (those described in this document), it is recommended to use a DPL file that does not have any networking or infrastructure objects inside it (DPNI, DPMAC, DPCON, DPIO, and so on), but only management objects (DPMCPs and root container).

Application Note

Such approach eliminates any types of configuration errors that may appear with multiple network interfaces that are configured to allocate as many resources as possible. For example, in a DPL, each DPNI has 8 traffic classes (each traffic class consumes 64 CTLU entries - 8 \* 64 CTLU entries per interface) and 16 Rx queues (each queue belongs to a DPCON with 2 or 8 work queue channels). Other networking objects (DPDMUX, L2SW) may be also present.

After the Linux OS boots, errors may occur in a context like this due to insufficient resources (insufficient CTLU memory and insufficient work queue channels), if the resources defined for each networking component are not computed carefully. This leads to extra debugging effort together with the initial troubleshooting context.

That is why a minimal DPL should be deployed on the LX2 target.

The following snippet shows the content of a minimal DPL or an "empty DPL". This DPL is used for all the debugging use cases described in the following sections:

```

/dts-v1/;

/ {

dpl-version = <10>;

/*****************

* Containers

************************

containers {

dprc@1 {

compatible = "fsl,dprc";

parent = "none";

options = "DPRC CFG OPT SPAWN ALLOWED" , "DPRC CFG OPT ALLOC ALLOWED",

"DPRC_CFG_OPT_IRQ_CFG_ALLOWED";

objects {

/* -----*/

obj set@dpmcp {

type = "dpmcp";

ids = <1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33

34 35 36 37 38 39 40>;

};

};

};

};

************

*************************

/* ----*/

dpmcp@1 {

compatible="fsl,dpmcp";

};

dpmcp@2 {

compatible="fsl,dpmcp";

};

dpmcp@3 {

compatible="fsl,dpmcp";

};

dpmcp@4 {

compatible="fsl,dpmcp";

dpmcp@5 {

compatible="fsl,dpmcp";

};

dpmcp@6 {

compatible="fsl,dpmcp";

};

dpmcp@7 {

```

```

compatible="fsl,dpmcp";

};

dpmcp@8 {

compatible="fsl,dpmcp";

};

dpmcp@9 {

compatible="fsl,dpmcp";

dpmcp@10 {

compatible="fsl,dpmcp";

};

dpmcp@11 {

compatible="fsl,dpmcp";

dpmcp@12 {

compatible="fsl,dpmcp";

};

dpmcp@13 {

compatible="fsl,dpmcp";

dpmcp@14 {

compatible="fsl,dpmcp";

};

dpmcp@15 {

compatible="fsl,dpmcp";

};

dpmcp@16 {

compatible="fsl,dpmcp";

};

dpmcp@17 {

compatible="fsl,dpmcp";

};

dpmcp@18 {

compatible="fsl,dpmcp";

dpmcp@19 {

compatible="fsl,dpmcp";

dpmcp@20 {

compatible="fsl,dpmcp";};

dpmcp@21 {

compatible="fsl,dpmcp";};

dpmcp@22 {

compatible="fsl,dpmcp"; );

dpmcp@23 {

compatible="fsl,dpmcp";};

dpmcp@24 {

compatible="fsl,dpmcp";};

dpmcp@25 {

compatible="fsl,dpmcp";};

dpmcp@26 {

compatible="fsl,dpmcp";};

dpmcp@27 {

compatible="fsl,dpmcp";};

dpmcp@28 {

compatible="fsl,dpmcp"; );

dpmcp@29 {

compatible="fsl,dpmcp";};

dpmcp@30 {

compatible="fsl,dpmcp";);

```

40 / 82

```

dpmcp@31 {

compatible="fsl,dpmcp"; );

dpmcp@32 {

compatible="fsl,dpmcp"; );

dpmcp@33 {

compatible="fsl,dpmcp"; };

dpmcp@34 {

compatible="fsl,dpmcp"; );

dpmcp@35 {

compatible="fsl,dpmcp"; );

dpmcp@36 {

compatible="fsl,dpmcp"; };

dpmcp@37 {

compatible="fsl,dpmcp"; );

dpmcp@38{

compatible="fsl,dpmcp"; };

dpmcp@39 {

compatible="fsl,dpmcp"; );

dpmcp@40 {

compatible="fsl,dpmcp"; );

};

};

```

Generate the DPL binary blob from the above source and write it to the target board. This document does not describe any build steps. The steps are described here or in the *Layerscape Software Development Kit User Guide*.

The following snippets describe the steps for booting the Linux OS with an empty DPL. They show how to create a network interface and dump the running configuration into an output file that can be used as a final DPL:

```

#after the empty DPL has been deployed on the target, reboot. #boot the MC firmware

fsl-mc: Booting Management Complex ... SUCCESS