# AN13540

LPC553x/LPC55S3x High-Speed Comparator - Evaluation of Basic Features Rev. 2 — 23 August 2023 Application note

#### **Document Information**

| Information | Content                                                                                                                                                                             |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Keywords    | AN13540, HSCMP, LPC553x/LPC55S3x                                                                                                                                                    |

| Abstract    | This application note describes various design criteria that system designers should consider when implementing HSCMP designs with the LPC553x/LPC55S3x family of microcontrollers. |

# 1 Introduction

This application note describes various design criteria that system designers should consider when implementing HSCMP designs with the LPC553x/LPC55S3x family of microcontrollers. This application note describes the critical parts of an HSCMP subsystem and its interconnections with related MCU peripheral modules, particularly those related to fast system protection (overcurrent or overvoltage protection).

This application note deals with basic comparator features of the LPC553x/LPC55S3x device. It presents possibilities to set up and evaluate the HSCMP module for real-time control applications.

This document is useful for engineers who want to discover internal peripheral interconnection possibilities and use cases of the HSCMP module. The software package with the example is in the NXP MCUXpresso IDE. FreeMASTER real-time debugger is used for application monitoring and control. The examples in this application note are implemented on the LPCxpresso55S36 EVK.

# **1.1 Introduction to HSCMP**

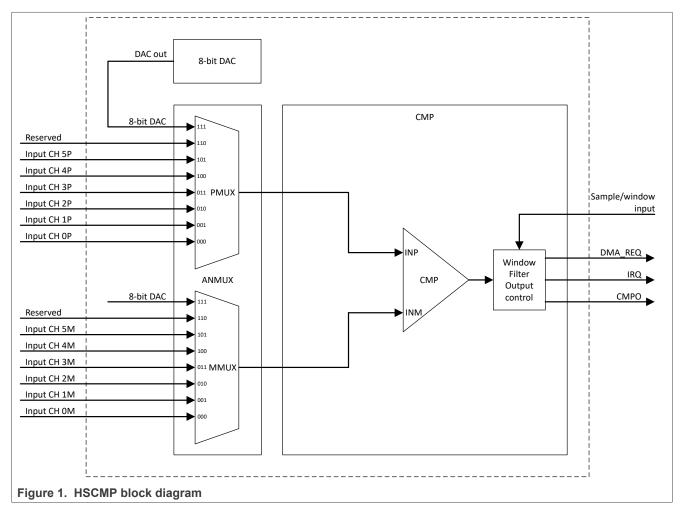

The High-Speed Comparator (HSCMP) module provides a circuit to compare two analog input voltages. It includes a comparator (CMP), 8-bit DAC, and an analog mux for each comparator input.

The CMP can operate across the full range of the supply voltage, which is known as a rail-to-rail operation. The DAC is a 256-tap resistor ladder network that provides a selectable voltage reference for applications that

require a voltage reference. The 256-tap resistor ladder network divides the supply reference (Vin) into 256 voltage levels. An 8-bit digital signal input selects the output voltage level, which varies from Vin to Vin/256. Vin can be selected from two voltage sources, vrefh0 and vrefh1. The HSCMP's internal DAC output is available as an on-chip internal signal only. It is not available for an external device pin. An internal 8-bit DAC is connected to both input muxes. It is also possible to connect a 12-bit DAC, which is available on specific input channels (see the following sections).

### 1.2 HSCMP features

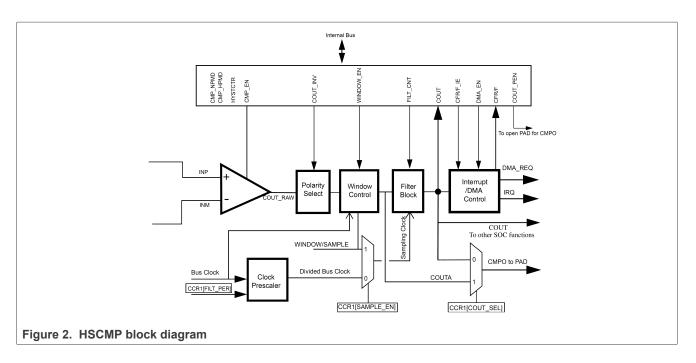

The features of the HSCMP module include the following:

- Two MUXes to select input signal from 8 channels

- Multiple operation modes to produce a wide range of outputs, such as:

- Sampled

- Windowed, which is ideal for certain PWM zero-crossing-detection applications

- Digitally filtered

- Advanced feature for window and sample:

- WINDOW/SAMPLE signal can be inverted

- Window can be closed by COUT rising, falling, or both edges

- User can define COUT level when window is closed

- Selectable performance levels: nano-power mode, low-power (speed) mode, high-power (speed) mode

- Programmable hysteresis control

- · Selectable inversion on comparator output

- · External hysteresis can be used at the same time as the output filter is used for internal functions

- Interrupt and DMA support

- Trigger mode

- Includes 8-bit resolution DAC

- · Selectable supply reference source for DAC

- · Configurable low- or high-power mode for DAC

HSCMP is intended for real-time control applications and fast-response use cases, such as overcurrent detection. It is possible to propagate a hardware compare event to disable the PWM, so the HSCMP acts as a hardware overcurrent protection. It could also be used for level-crossing detection of signals in various applications, such as power converters. The HSCMP compare event can also restart the PWM.

AN13540

# 2 Pin configuration

The analog mode of the HSCMP multiplexer input pins must be set. For more details, see the "I/O Pin Configuration (IOCON)" chapter in the reference manual (pin multiplexing and IOCON register description) and the low-level software examples below. Table 1 summarizes all HSCMP pins on the LPC553x/LPC55S3x device and their availability on the HSCMP input mux. Inputs and indexes are identical on both positive and negative muxes and registers HSCMP\_CCR2\_MSEL and HSCMP\_CCR2\_PSEL.

| Input MUX index | HSCMP0                           | HSCMP1                         | HSCMP2             |

|-----------------|----------------------------------|--------------------------------|--------------------|

| 0               | HSCMP0_IN0 PIO0_24               | HSCMP1_IN0 PIO0_7              | HSCMP2_IN0 PIO0_17 |

| 1               | HSCMP0_IN1 PIO1_12               | HSCMP1_IN1 DAC0_OUT<br>PIO1_22 | HSCMP2_IN1 PIO1_23 |

| 2               | Unconnected                      | Unconnected                    | Unconnected        |

| 3               | HSCMP0_IN3 PIO1_5                | HSCMP1_IN3 PIO1_10             | Unconnected        |

| 4               | HSCMP0_IN4 OPAMP0_<br>OUT PIO1_9 | OPAMP1_OUT                     | OPAMP2_OUT         |

| 5               | DAC0_OUT PIO1_22                 | HSCMP1_IN5 DAC1_OUT<br>PIO1_19 | DAC2_OUT           |

| 6               | Reserved                         | Reserved                       | Reserved           |

| 7               | HSCMP0 DAC                       | HSCMP1 DAC                     | HSCMP2 DAC         |

# 2.1 Comparator evaluation

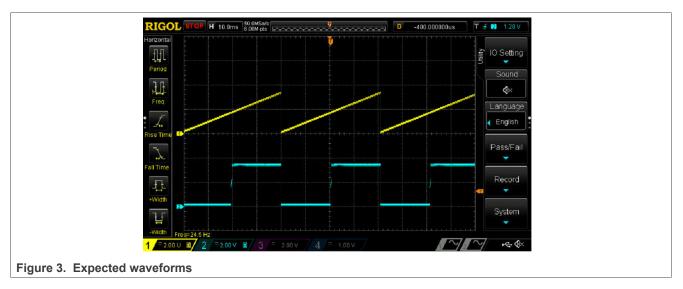

This application note and evaluation software describes basic functionality. The example demonstrates a comparison of two signals: the sawtooth generated by the 12-bit DAC and the constant voltage reference generated by the HSCMP internal 8-bit DAC. The result of the HSCMP comparison can be observed on the output pin. You can invert the output logic and set different threshold values (internal 8-bit DAC, external 12-bit

DAC, or MCU input pins signals according to <u>Table 1</u>). MCUXpresso, LPC553x/LPC55S3x SDK package, and the FreeMASTER tool must be installed.

To run the SDK HSCMP example, perform the following steps:

- 1. Unzip the example to your hard drive location.

- 2. Import the example into the MCUXpresso IDE.

- 3. Build the example.

- 4. Flash the example.

- 5. Start the FreeMASTER HSCMP project.

- 6. Click the "Run" button.

- 7. Set the variables (especially the threshold value) in the runtime using the FreeMASTER real-time debugger. The result can be monitored using an oscilloscope.

The oscilloscope can be connected to J10-11 on LPCXpresso55S36 to monitor the comparator output and a second probe can be connected to J10-9 to observe the 12-bit DAC (see Figure 3). External signal connected to J9-9 (HSCMP0\_IN3) could be connected instead of the 12-bit DAC output (the reconfiguration of HSCMP MUX must be done in the source file). When evaluating the software example, the expected default waveforms should look like the signals in Figure 3.

# **3** Using the HSCMPs for overcurrent protection

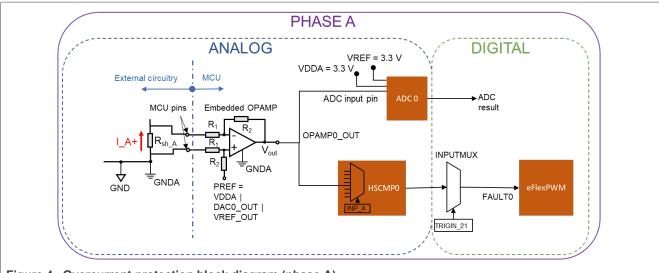

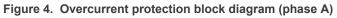

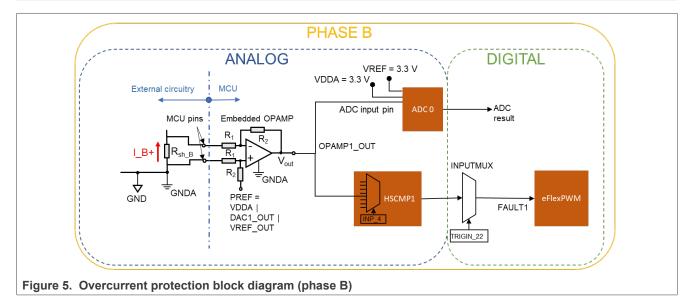

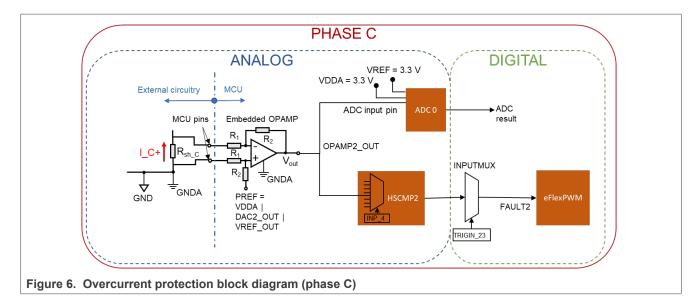

The following schematics show a typical 3-shunt configuration for motor-control applications.  $R_{sh_{<x>}}$  is a shunt resistor in a low-side current-sensing configuration. The voltage drop across this resistor is amplified by the internal variable-gain OPAMP.  $R_1$  and  $R_2$  are part of the internal resistor network and their values are, along with the positive reference voltage (PREF) source, configurable via the OPAMP\_CTR register.

The OPAMP output signal (OPAMP<x>\_OUT) is internally wired to ADCs, HSCMPs, and output pins. Depending on the particular OPAMP<x>\_OUT – HSCMP<y> input combination, an analog switch may require to be closed by setting the respective ASW0 or ASW1 bits in the IOCON module PIO registers. See the corresponding table in the reference manual.

The HSCMP positive and negative input signals are configurable via the HSCMP CCR2 register.

The HSCMP output signal is routed via the INPUTMUX module to the fault input of the related eFlexPWM submodule (see the PWM0\_FAULT0 – PWM0\_FAULT3 registers of the INPUTPUX).

# AN13540

LPC553x/LPC55S3x High-Speed Comparator - Evaluation of Basic Features

# 3.1 Overcurrent protection design guideline

The OPAMPn\_OUT<sub>max</sub> voltage corresponding to the maximal current could be determined using the following formula:

$$OPAMPnOUT_{max} = (I_{max} * R_{sh} * GAIN) + PREF$$

[V]

Please note that in the depicted scenario, the current direction convention is such that the overcurrent flowing from the DC-Bus to the GND generates a negative voltage drop across the shunt resistor, therefore OPAMPnOUT<sub>max</sub> < PREF.

This calculated value presents the comparator reference voltage, which may be generated by the internal 8-bit DAC of the HSCMP. Alternatively, an external 12-bit DAC could be set as the reference source. The comparator reference voltage should then be routed to the INM input of the comparator. The OPAMPn\_OUT signal should be connected to the INP input pin. The HSCMP configuration example (using the internal DAC) is as follows:

```

/* Port 2, pin 14 (OPAMP1 OUT) to HSCMP1 IN4 - close the analog switch */

IOCON PinMuxSet(IOCON, 2, 14, IOCON FUNCO | IOCON ANALOG EN | (1U << 10 ));

/* Power up the CMP bias circuitry */

POWER_DisablePD(kPDRUNCFG_PD_CMPBIAS);

/* Power up the HSCMP and its internal DAC */

POWER DisablePD(kPDRUNCFG PD HSCMP1);

POWER DisablePD(kPDRUNCFG PD HSCMP1 DAC);

HSCMP1->CCR1 = (1U << 5) //* Enable comparator output*/

(1U << 4);

/* Use COUTA (unfiltered comparator output) */

HSCMP1->CCR2 = (OU << 28) | /* INM - 8-bit DAC */

(1U << 24) | /* INP - Analog 8-1 mux */

(7U << 20) | /* MSEL - 8-bit DAC */

| /* PSEL - OPAMP1 OUT */

(4U << 16)

(1U << 0);

/* High power mode */

/* Set DAC OUT to 1.225V (2.5A current through 0.020 Ohm shunt) */

HSCMP1->DCR = (94U << 16) | /* (3.3V / 256) * (94 + 1) = 1.224 V */

(1U << 15) | /* DAC output enable */

```

#### AN13540

```

(1U << 1) | /* High power mode enabled */

(1U << 0);

/* DAC enable */

/* HSCMP enable */

HSCMP1->CCR0 = 1U;

```

The output of the HSCMP should be routed (via the INPUTMUX module) to the respective FAULT input of the PWM submodule responsible for generating the corresponding phase PWM signals. The INPUTMUX configuration example is as follows:

```

/* Separate fault per each OPAMP */

INPUTMUX->PWM0 FAULT[0] = 21U;

/* PWM0 fault 0 = HSCMP0 */

INPUTMUX->PWM0 FAULT[1] = 22U;

/* PWM0 fault 1 = HSCMP1 */

INPUTMUX->PWM0 FAULT[2] = 23U;

/* PWM0 fault 2 = HSCMP2 */

```

The FAULT signal is edge-sensitive and its polarity is configurable. The PWM must be configured to detect the fault signal and react appropriately. The FlexPWM fault-handling configuration example is as follows:

```

/* Separate fault per each OPAMP */

PWMO - SM[0].DISMAP[0] = 0xF777U;

PWMO - SM[1].DISMAP[0] = 0xF777U;

PWMO - SM[2].DISMAP[0] = 0xF777U;

PWMO ->SM[3].DISMAP[0] = 0xF777U;

/* PWM fault filter - 3 Fast periph. clocks sample rate, 5 agreeing samples to

activate */

PWMO->FFILT |= PWM FFILT FILT PER(2);

PWMO->FFILT |= PWM FFILT FILT CNT(2);

/* All interrupts disabled, safe manual fault clearing */

PWM0->FCTRL &= ~(PWM FCTRL FLVL MASK | PWM FCTRL FAUTO MASK |

PWM FCTRL FSAFE MASK | PWM FCTRL FIE MASK);

/* Clear FCTRL register prior further settings */

PWMO->FCTRL |= PWM FCTRL FIE(OU);

/* FAULT 0 & FAULT 1 - Interrupt disable */

/* Internal OPAMP fault signals are active low. */

PWMO->FCTRL |= PWM FCTRL FLVL(0x0U);

PWMO->FCTRL |= PWM FCTRL FAUTO(0U);

PWMO->FCTRL |= PWM FCTRL FSAFE(0xFU);

```

# 4 Note about the source code in the document

Example code shown in this document has the following copyright and BSD-3-Clause license:

Copyright 2023 NXP Redistribution and use in source and binary forms, with or without modification, are permitted provided that the following conditions are met:

- 1. Redistributions of source code must retain the above copyright notice, this list of conditions and the following disclaimer.

- 2. Redistributions in binary form must reproduce the above copyright notice, this list of conditions and the following disclaimer in the documentation and/or other materials must be provided with the distribution.

- 3. Neither the name of the copyright holder nor the names of its contributors may be used to endorse or promote products derived from this software without specific prior written permission.

THIS SOFTWARE IS PROVIDED BY THE COPYRIGHT HOLDERS AND CONTRIBUTORS "AS IS" AND ANY EXPRESS OR IMPLIED WARRANTIES, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES

OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE ARE DISCLAIMED. IN NO EVENT SHALL THE COPYRIGHT HOLDER OR CONTRIBUTORS BE LIABLE FOR ANY DIRECT, INDIRECT, INCIDENTAL, SPECIAL, EXEMPLARY, OR CONSEQUENTIAL DAMAGES (INCLUDING, BUT NOT LIMITED TO, PROCUREMENT OF SUBSTITUTE GOODS OR SERVICES; LOSS OF USE, DATA, OR PROFITS; OR BUSINESS INTERRUPTION) HOWEVER CAUSED AND ON ANY THEORY OF LIABILITY, WHETHER IN CONTRACT, STRICT LIABILITY, OR TORT (INCLUDING NEGLIGENCE OR OTHERWISE) ARISING IN ANY WAY OUT OF THE USE OF THIS SOFTWARE, EVEN IF ADVISED OF THE POSSIBILITY OF SUCH DAMAGE.

# 5 Revision history

Table 2 summarizes the changes to this document.

#### **Revision history**

| Revision number | Release date    | Description                                    |

|-----------------|-----------------|------------------------------------------------|

| 0               | 27 January 2022 | Initial release                                |

| 1               | 20 May 2022     | Replaced LPC55S36 with LPC553x/LPC55S3x        |

| 2               | 23 August 2023  | Replaced Figure 1 and several smaller updates. |

# 6 Legal information

### 6.1 Definitions

**Draft** — A draft status on a document indicates that the content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included in a draft version of a document and shall have no liability for the consequences of use of such information.

# 6.2 Disclaimers

Limited warranty and liability — Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information. NXP Semiconductors takes no responsibility for the content in this document if provided by an information source outside of NXP Semiconductors.

In no event shall NXP Semiconductors be liable for any indirect, incidental, punitive, special or consequential damages (including - without limitation - lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory.

Notwithstanding any damages that customer might incur for any reason whatsoever, NXP Semiconductors' aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the Terms and conditions of commercial sale of NXP Semiconductors.

**Right to make changes** — NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

Suitability for use — NXP Semiconductors products are not designed, authorized or warranted to be suitable for use in life support, life-critical or safety-critical systems or equipment, nor in applications where failure or malfunction of an NXP Semiconductors product can reasonably be expected to result in personal injury, death or severe property or environmental damage. NXP Semiconductors and its suppliers accept no liability for inclusion and/or use of NXP Semiconductors products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.

**Applications** — Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

Customers are responsible for the design and operation of their applications and products using NXP Semiconductors products, and NXP Semiconductors accepts no liability for any assistance with applications or customer product design. It is customer's sole responsibility to determine whether the NXP Semiconductors product is suitable and fit for the customer's applications and products planned, as well as for the planned application and use of customer's third party customer(s). Customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products.

NXP Semiconductors does not accept any liability related to any default, damage, costs or problem which is based on any weakness or default in the customer's applications or products, or the application or use by customer's third party customer(s). Customer is responsible for doing all necessary testing for the customer's applications and products using NXP Semiconductors products in order to avoid a default of the applications and the products or of the application or use by customer's third party customer(s). NXP does not accept any liability in this respect.

**Export control** — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from competent authorities.

**Evaluation products** — This product is provided on an "as is" and "with all faults" basis for evaluation purposes only. NXP Semiconductors, its affiliates and their suppliers expressly disclaim all warranties, whether express, implied or statutory, including but not limited to the implied warranties of non-infringement, merchantability and fitness for a particular purpose. The entire risk as to the quality, or arising out of the use or performance, of this product remains with customer.

In no event shall NXP Semiconductors, its affiliates or their suppliers be liable to customer for any special, indirect, consequential, punitive or incidental damages (including without limitation damages for loss of business, business interruption, loss of use, loss of data or information, and the like) arising out the use of or inability to use the product, whether or not based on tort (including negligence), strict liability, breach of contract, breach of warranty or any other theory, even if advised of the possibility of such damages.

Notwithstanding any damages that customer might incur for any reason whatsoever (including without limitation, all damages referenced above and all direct or general damages), the entire liability of NXP Semiconductors, its affiliates and their suppliers and customer's exclusive remedy for all of the foregoing shall be limited to actual damages incurred by customer based on reasonable reliance up to the greater of the amount actually paid by customer for the product or five dollars (US\$5.00). The foregoing limitations, exclusions and disclaimers shall apply to the maximum extent permitted by applicable law, even if any remedy fails of its essential purpose.

**Translations** — A non-English (translated) version of a document, including the legal information in that document, is for reference only. The English version shall prevail in case of any discrepancy between the translated and English versions.

Security — Customer understands that all NXP products may be subject to unidentified vulnerabilities or may support established security standards or specifications with known limitations. Customer is responsible for the design and operation of its applications and products throughout their lifecycles to reduce the effect of these vulnerabilities on customer's applications and products. Customer's responsibility also extends to other open and/or proprietary technologies supported by NXP products for use in customer's applications. NXP accepts no liability for any vulnerability. Customer should regularly check security updates from NXP and follow up appropriately. Customer shall select products with security features that best meet rules,

regulations, and standards of the intended application and make the ultimate design decisions regarding its products and is solely responsible for compliance with all legal, regulatory, and security related requirements concerning its products, regardless of any information or support that may be provided by NXP.

NXP has a Product Security Incident Response Team (PSIRT) (reachable at <u>PSIRT@nxp.com</u>) that manages the investigation, reporting, and solution release to security vulnerabilities of NXP products.

**NXP B.V.** - NXP B.V. is not an operating company and it does not distribute or sell products.

# 6.3 Trademarks

Notice: All referenced brands, product names, service names, and trademarks are the property of their respective owners.

NXP — wordmark and logo are trademarks of NXP B.V.

# AN13540

LPC553x/LPC55S3x High-Speed Comparator - Evaluation of Basic Features

# Contents

| Introduction                            | 2                                                                                                                                                                                                                                                       |

|-----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Introduction to HSCMP                   | 2                                                                                                                                                                                                                                                       |

| HSCMP features                          | 3                                                                                                                                                                                                                                                       |

| Pin configuration                       | 4                                                                                                                                                                                                                                                       |

| -                                       |                                                                                                                                                                                                                                                         |

| Using the HSCMPs for overcurrent        |                                                                                                                                                                                                                                                         |

| protection                              | 5                                                                                                                                                                                                                                                       |

| Overcurrent protection design guideline | 7                                                                                                                                                                                                                                                       |

| Note about the source code in the       |                                                                                                                                                                                                                                                         |

| document                                | 8                                                                                                                                                                                                                                                       |

| Revision history                        | 9                                                                                                                                                                                                                                                       |

| Legal information                       |                                                                                                                                                                                                                                                         |

|                                         | Introduction to HSCMP<br>HSCMP features<br>Pin configuration<br>Comparator evaluation<br>Using the HSCMPs for overcurrent<br>protection<br>Overcurrent protection design guideline<br>Note about the source code in the<br>document<br>Revision history |

Please be aware that important notices concerning this document and the product(s) described herein, have been included in section 'Legal information'.

© 2023 NXP B.V.

All rights reserved.

For more information, please visit: http://www.nxp.com