NXP Semiconductors Application Note

# i.MX 6ULZ Migration Guide

Migrating from i.MX 6ULL to i.MX 6ULZ

# 1. Introduction

This application note provides an introduction to the i.MX 6ULZ architecture by highlighting the differences from i.MX 6ULL series processor upon which it is based. This migration guide is useful for the developers that migrate from the i.MX 6ULL to the i.MX 6ULZ.

#### Contents

| 1. | Intro                  | oduction                     |  |

|----|------------------------|------------------------------|--|

|    |                        | i.MX 6ULZ processor overview |  |

| 2. | Feature change summary |                              |  |

|    | 2.1.                   | BSP support                  |  |

|    | 2.2.                   | Module change list           |  |

|    | 2.3.                   | PINMUX change list           |  |

|    |                        | ision History                |  |

## 1.1. i.MX 6ULZ processor overview

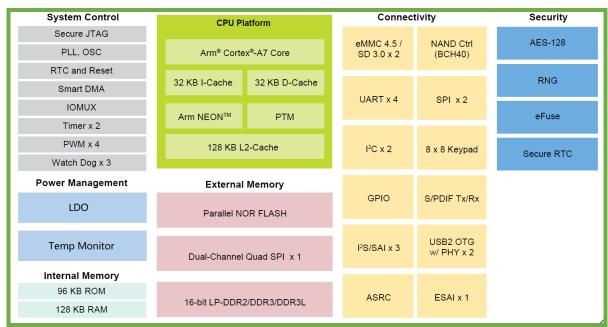

The i.MX 6ULZ processor is a high-performance, ultra-efficient processor featuring an advanced implementation of a single Arm<sup>®</sup> Cortex<sup>®</sup>-A7 core, which operates at speed up to 900 MHz. It is an ultra-low-cost extension of the i.MX 6ULL family product, which offers high performance processing with a high degree of functional integration and targeted towards the growing market of connected devices.

Its target applications contain more about following:

- Computing Engine

- Consumer Electronics

- Audio

- Voice Control

The i.MX 6ULZ application processors includes full audio suite: ESAI, I<sup>2</sup>S x 3, S/PDIF, and an integrated power management module that reduces the complexity of an external power supply and simplifies power sequencing. Each processor in this family provides various memory interfaces, including 16-bit LPDDR2, DDR3, DDR3L, raw and managed NAND flash, NOR flash, eMMC, Quad SPI and a wide range of other interfaces for connecting peripherals such as WLAN, Bluetooth<sup>®</sup>, GPS, displays and camera sensors. The i.MX 6ULZ is supported by discrete component power circuitry.

Figure 1. i.MX6ULZ Application Processor Block Diagram

## 2. Feature change summary

### 2.1. BSP support

The i.MX 6ULZ is supported by the Linux\_4.14.62\_1.0.0 BSP release.

#### NOTE

The machine name of 6ULZ is different from 6ULL when building Yocto Project. The dtb file names are also different when running Yocto Project.

### 2.2. Module change list

This section summarizes the architectural changes of the i.MX 6ULZ with respect to the i.MX 6ULL. The security features of 6ULZ are same with MCIMX6Y2.

| Feature                    | MCIMX6Y0                                                                    | MCIMX6Z0                     | MCIMX6Y1                                     | MCIMX6Y2                                     |

|----------------------------|-----------------------------------------------------------------------------|------------------------------|----------------------------------------------|----------------------------------------------|

| Sub Family                 | 6ULL Base                                                                   | 6ULZ                         | 6ULZ 6ULL General Purpose 1                  |                                              |

| Core                       | ARM Cortex-A7                                                               | ARM Cortex-A7                | ARM Cortex-A7                                | ARM Cortex-A7                                |

| Speed                      | 528 MHz                                                                     | Up to 900MHz                 | 528 MHz                                      | Up to 900 MHz                                |

| Cache                      | 32 KB-I, 32KB-D<br>128KB L2                                                 | 32 KB-I, 32KB-D<br>128 KB L2 | 32 KB-I, 32KB-D<br>128 KB L2                 | 32 KB-I, 32KB-D<br>128 KB L2                 |

| OCRAM                      | 128 KB                                                                      | 128 KB                       | 128 KB                                       | 128 KB                                       |

| DRAM                       | 16-bit LP-DDR2, DDR3/DDR3L                                                  | 16-bit LP-DDR2, DDR3/DDR3L   | 16-bit LP-DDR2, DDR3/DDR3L                   | 16-bit LP-DDR2, DDR3/DDR3L                   |

| eFuse for Customer         | 256-bit                                                                     | 256-bit                      | 256-bit                                      | 256-bit                                      |

| NAND (BCH40)               | Yes                                                                         | Yes                          | Yes                                          | Yes                                          |

| Parallel Nor/EBI           | Yes                                                                         | Yes                          | Yes                                          | Yes                                          |

| Ethernet                   | 10/100 MB x 1                                                               | None                         | 10/100 MB x 1                                | 10/100 MB x 2                                |

| USB with PHY               | OTG, HS/FS x 1                                                              | OTG, HS/FS x 2               | OTG, HS/FS x 2                               | OTG, HS/FS x 2                               |

| CAN                        | 0                                                                           | 0                            | 1                                            | 2                                            |

| Graphic                    | None                                                                        | None                         | None                                         | PxP                                          |

| CSI                        | None                                                                        | None                         | None                                         | 16-bit Parallel CSI                          |

| LCD                        | None                                                                        | None                         | None                                         | 24-bit Parallel LCD                          |

| Touch Screen<br>Controller | None                                                                        | None                         | None                                         | Yes                                          |

| QSPI                       | 1                                                                           | 1                            | 1                                            | 1                                            |

| SDIO                       | 2                                                                           | 2                            | 2                                            | 2                                            |

| UART                       | 4                                                                           | 4                            | 8                                            | 8                                            |

| IIC                        | 2                                                                           | 2                            | 4                                            | 4                                            |

| SPI                        | 2                                                                           | 2                            | 4                                            | 4                                            |

| I2S/SAI                    | 1                                                                           | 3                            | 3                                            | 3                                            |

| ESAI                       | 0                                                                           | 1                            | 1                                            | 1                                            |

| S/PDIF                     | 1                                                                           | 1                            | 1                                            | 1                                            |

| Timer/PWM                  | Timer x2, PWM x4                                                            | Timer x2, PWM x4             | Timer x4, PWM x8                             | Timer x4, PWM x8                             |

| 12-bit ADC                 | 1 x 8ch                                                                     | None                         | 1 x 8ch                                      | 2 x 8ch                                      |

| Security                   | No Security<br>(The encryption/decryption functions<br>in DCP are disabled) | Basic Security               | Basic Security                               | Basic Security                               |

| Keyboard (8 x 8)           | Yes                                                                         | Yes                          | Yes                                          | Yes                                          |

| Temperature                | -40°C to 105°C (Tj)<br>-0°C to 95°C (Tj)                                    | -0° C to 95° C (Tj)          | -40 °C to 105 °C (Tj)<br>-0 °C to 95 °C (Tj) | -40 °C to 105 °C (Tj)<br>-0 °C to 95 °C (Tj) |

#### Table 1. Architectural changes

## 2.3. PINMUX change list

#### **Revision history**

According to the module change list, there are several modules that have been removed or reduced in 6ULZ-MCIMX6Z0 compare to MCIMX6Y2. Including Ethernet, CAN, Graphic, CSI, LCD, UART, I<sup>2</sup>C, SPI, Timer/PWM and ADC.

Detailed PINMUX change can be found in the data sheet of i.MX 6ULZ named i.MX 6ULZ Applications Processors for Consumer Products. Meanwhile, the i.MX Pins Tool can also be a good reference.

# 3. Revision history

|                 | Table 2. | Revision history |                     |

|-----------------|----------|------------------|---------------------|

| Revision number |          | Date             | Substantive changes |

| 0               |          | 10/2018          | Initial release     |

| 1               |          | 03/2020          | Updated Table 1     |

#### How to Reach Us:

Home Page: nxp.com

Web Support: nxp.com/support Information in this document is provided solely to enable system and software implementers to use NXP products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits based on the information in this document. NXP reserves the right to make changes without further notice to any products herein.

NXP makes no warranty, representation, or guarantee regarding the suitability of its products for any particular purpose, nor does NXP assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in NXP data sheets and/or specifications can and do vary in different applications, and actual performance may vary over time. All operating parameters, including "typicals," must be validated for each customer application by customer's technical experts. NXP does not convey any license under its patent rights nor the rights of others. NXP sells products pursuant to standard terms and conditions of sale, which can be found at the following address: nxp.com/SalesTermsandConditions.

While NXP has implemented advanced security features, all products may be subject to unidentified vulnerabilities. Customers are responsible for the design and operation of their applications and products to reduce the effect of these vulnerabilities on customer's applications and products, and NXP accepts no liability for any vulnerability that is discovered. Customers should implement appropriate design and operating safeguards to minimize the risks associated with their applications and products.

NXP, NXP, the NXP logo, NXP SECURE CONNECTIONS FOR A SMARTER WORLD, COOLFLUX, EMBRACE, GREENCHIP, HITAG, I2C BUS, ICODE, JCOP, LIFE VIBES, MIFARE, MIFARE CLASSIC, MIFARE DESFire, MIFARE PLUS, MIFARE FLEX, MANTIS, MIFARE ULTRALIGHT, MIFARE4MOBILE, MIGLO, NTAG, ROADLINK, SMARTLX, SMARTMX, STARPLUG, TOPFET, TRENCHMOS, UCODE, Freescale, the Freescale logo, AltiVec, C-5, CodeTEST, CodeWarrior, ColdFire, ColdFire+, C-Ware, the Energy Efficient Solutions logo, Kinetis, Layerscape, MagniV, mobileGT, PEG, PowerQUICC, Processor Expert, QorlQ, QorlQ Qonverge, Ready Play, SafeAssure, the SafeAssure logo, StarCore, Symphony, VortiQa, Vybrid, Airfast, BeeKit, BeeStack, CoreNet, Flexis, MXC, Platform in a Package, QUICC Engine, SMARTMOS, Tower, TurboLink, and UMEMS, EdgeScale, EdgeLock, eIQ, and Immersive 3D are trademarks of NXP B.V. All other product or service names are the property of their respective owners. Arm, AMBA, Arm Powered, Artisan, Cortex, Jazelle, Keil, SecurCore, Thumb, TrustZone, and µVision are registered trademarks of Arm Limited (or its subsidiaries) in the EU and/or elsewhere. Arm7, Arm9, Arm11, big.LITTLE, CoreLink, CoreSight, DesignStart, Mali, Mbed, NEON, POP, Sensinode, Socrates, ULINK and Versatile are trademarks of Arm Limited (or its subsidiaries) in the EU and/or elsewhere. All rights reserved. Oracle and Java are registered trademarks of Oracle and/or its affiliates. The Power Architecture and Power.org word marks and the Power and Power.org logos and related marks are trademarks and service marks licensed by Power.org.

© 2018-2020 NXP B.V.

Document Number: AN12264 Rev. 1 03/2020

# arm