### AN13530 LPC553x/LPC55S3x Low-power Modes and Wake-up Time Rev. 2 — 4 September 2023

**Application note**

### **Document Information**

| Information | Content                                                                                                                                                                                               |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Keywords    | AN13530, LPC55S3x/LPC553x, low-power mode, wake-up time                                                                                                                                               |

| Abstract    | This application note introduces various low-power modes of the LPC553x/LPC55S3x series, the software APIs details to enter in the low-power mode, and a wake-up source used for each low-power mode. |

### 1 Introduction

LPC553x/LPC55S3x is an Arm Cortex-M33-based microcontroller for embedded applications. The family offers a rich set of peripherals with a feature of low power consumption. For more details on the LPC553x/LPC55S3x MCU, see LPC5500 Cortex-M33.

This application note introduces various low-power modes of the LPC553x/LPC55S3x series, the software APIs details to enter in the low-power mode, and a wake-up source used for each low-power mode. This document also describes the hardware and software environment as well as a procedure to measure supply current and wake-up time for each low-power mode.

This application note explains:

- All low-power modes in LPC553x/LPC55S3x

- · Entry and wake-up implementations for low-power modes

- Steps to measure current and wake-up time for each low-power mode

### 2 Low-power modes

LPC553x/LPC55S3x supports four reduced power modes: Sleep, Deep sleep, Power down, and Deep power down.

These modes can be activated by power library APIs from the SDK software package.

Power usage is controlled by settings in the register within the SYSCON block, regulator settings controlled via the power library APIs, and the operating mode of the CPU. The following modes are supported in order from maximum to minimum power consumption.

- Section 2.1

- <u>Section 2.2</u>

- Section 2.3

- <u>Section 2.4</u>

- <u>Section 2.5</u>

### 2.1 Active mode

The device is in the Active mode after any chip-level reset. The following reset values determine the default dynamic power consumption:

- Power Management Controller registers, PDRUNCFG0/1 (For details, see "Chapter 36 Power Management Controller" in *LPC553x Reference Manual* (document <u>LPC553xRM</u>))

- SYSCON registers AHBCLKCTRL0/1/2/3 and AUTOCLKGATEOVERRIDE (For details, see "Chapter 7 SYSCON" in *LPC553x Reference Manual* (document <u>LPC553xRM</u>)

In the Active mode, by default, the core logic supply source is the Low Drop-Out Regulator (LDO\_CORE). The user can switch to the DC-DC converter to gain better dynamic power efficiency via a set of functions provided in the power library: POWER SetCorePowerSource(...) and POWER GetCorePowerSource(...).

In the Active mode, it is possible to individually control all the SRAM instances power mode via the function POWER SRAMPowerModeControl(...) provided in the power library.

In the Active mode, when the device is in operation, it is possible to reduce the power consumption of the various peripherals that are not used (temporarily or permanently) by:

- Switching off their functional clock; see SYSCON registers AHBCLKCTRL0/1/2/3

- Activating the "automatic clock gating" feature; see SYSCON register AUTOCLKGATEOVERRIDE

• Switching off the entire module when possible; see Power Management Controller registers PDRUNCFG0 and PDRUNCFG1

The Active mode consumes the highest power among all power modes. All low-power modes can be invoked from this power mode.

### 2.2 Sleep mode

Sleep mode saves some power by stopping the Cortex-M33 CPU execution without affecting peripherals or requiring significant wake-up time. The clock to the CPU is shut off. Peripherals and memories are active and operational. CPU is stopped and execution of instructions is suspended until either a reset or an interrupt occurs.

Peripheral functions, if selected to be clocked in the AHBCLKCTRL registers, continue operation during Sleep mode and can generate interrupts to cause the processor to resume execution. Sleep mode only eliminates dynamic power used by the processor itself, memory systems and related controllers, and internal buses. The processor state and registers, peripheral registers, and internal SRAM values are maintained.

### 2.3 Deep sleep mode

In the Deep sleep mode, the full device remains powered, but flash and ROM are shut down, with the cost of a longer wake-up time compared to the Sleep mode. The system clock to the CPU is disabled as in the Sleep mode. Analog blocks are powered down by default but can be selected to keep running through the power API if needed as wake-up sources. The main clock and all peripheral clocks are disabled.

The Deep sleep mode eliminates power used by the analog peripherals and all dynamic power used by the CPU, its memory systems and related controllers, and internal buses. The CPU state and registers, peripheral registers, and internal SRAM values are maintained, and the logic levels of the pins remain static. All SRAM instances that are not configured to enter in the SRAM Deep sleep low-power mode keep the state they are in before entering the Deep sleep. This means that if a SRAM was in the Active state before entering the Deep sleep, it stays in the Active state during the Deep sleep and therefore it consumes more power.

Selected peripherals, such as GPIO group interrupts (GINT), USB Full speed, Flexcomms (SPI, I2C, USART), Widowed-Watchdog Timer, RTC, standard Counter/Timers can be left running in the Deep sleep mode. The oscillators, such as FRO1M, FRO32K, XTAL32K but also FRO192M (which delivers the 12 MHz and 96 MHz clocks), can also be left running.

Some peripherals can have DMA service during the Deep sleep mode without waking up the entire device.

### 2.4 Power-down mode

The Power-down mode turns off nearly all on-chip power consumption by:

- Eliminating power used by almost all analog modules and

- Shutting down the DC-DC and LDO\_CORE

This eliminates almost all digital peripherals power, with the cost of a longer wake-up time compared to the Deep sleep mode. FRO192M is disabled. The flash memory is also disabled. The clock to the CPU and peripherals is shut down and if not configured, the peripherals in the power domains PD\_SYSTEM and PD\_AO receive no internal clocks. All SRAM instances can be configured to maintain their internal states and all registers lose their internal states except those located in the power domains PD\_SYSTEM and PD\_AO. Any SRAM instance that is not configured to maintain its internal state loses it.

The Cortex-M33 CPU state and some critical peripherals, such as security controller, PRINCE, and analog controller are retained and the logic levels of the pins remain static. GPIO group interrupts (GINTO and GINT1), selected serial peripherals in Flexcomm3 (SPI, I2C, USART), RTC, OS event timers, and analog comparator can be left running to wake up the device.

When a wake-up event occurs, the Cortex-M33 CPU code execution resumes. It is the responsibility of the customer application to reconfigure all modules in the power domain core PD\_CORE (whose states have not been retained, for example all Flexcomm except Flexcomm3, SDMA, Power Quad, DMIC).

### 2.5 Deep Power-down mode

Deep Power-down mode shuts down virtually all on-chip power consumption, but requires a longer wake-up time (compared to the Power-down mode). For maximal power savings, the entire power domains PD\_CORE (CPU, DSP, Flexcomms, SDMA) and PD\_SYSTEM (Reset, Clocks, SYSCON, IOCON) are shut down. Only the Always-on power domain PD\_AO (PMU, PMC, RTC, and OS Event Timer) stays powered. Clocks are shut off to the entire chip device except for the RTC and the OS Event Timer, if they are needed. On wake-up, the device reboots.

During the Deep Power-down mode, the contents of some SRAM can be retained (software configured via the POWER\_EnterDeepPowerDown() low-power API) but registers (other than those in PMC, RTC, and OS Event Timer) are not retained. All functional pins are tri-stated in the Deep Power-down mode, except the 5 wake-up pins and the RESETN pin.

### 2.6 Low-power mode summary

The following table summarizes the power state of the different power domains according to the power modes.

| Power mode         | PD_CORE | PD_<br>SYSTEM | PD_AON | PD_MEM_0                    | PD_MEM_1                    | PD_MEM_2                    |

|--------------------|---------|---------------|--------|-----------------------------|-----------------------------|-----------------------------|

| Active             | ON      | ON            | ON     | ON                          | ON                          | ON                          |

| Sleep              | ON      | ON            | ON     | ON                          | ON                          | ON                          |

| Deep sleep         | ON      | ON            | ON     | Configurable <sup>[1]</sup> | Configurable <sup>[2]</sup> | Configurable <sup>[3]</sup> |

| Power down         | OFF     | ON            | ON     | Configurable                | Configurable                | Configurable                |

| Deep power<br>down | OFF     | OFF           | ON     | Configurable                | Configurable                | Configurable                |

Table 1. Power modes vs Power domains

[1] Depending on whether the RAM\_01 Deep sleep power mode (data retention) is required by the user via the relevant Power API function, this power domain is ON or OFF.

[2] Depending on whether the Deep sleep power mode (data retention) is required for one SRAM instance in this power domain by the user via the relevant Power API function, this power domain is ON or OFF.

[3] Depending on whether the RAM\_00 Deep sleep power mode (data retention) is required by the user via the relevant Power API function, this power domain is ON or OFF.

The following table summarizes the power state of the different peripherals according to the power modes.

| Table 2. Peripherals reduced power mod |

|----------------------------------------|

|----------------------------------------|

| Peripherals |                                     | De                                                    | Device low-power modes |                     |                                |

|-------------|-------------------------------------|-------------------------------------------------------|------------------------|---------------------|--------------------------------|

| Name        | Description                         | Sleep mode                                            | Deep sleep<br>mode     | Power-down<br>mode  | Deep<br>Power-<br>down<br>mode |

| DCDC        | Bulk DC-DC converter                | Same state as in Active mode                          | OFF                    | OFF                 | OFF                            |

| BIAS        | Analog references                   | ON                                                    | ON                     | Software configured | OFF                            |

| BODCORE     | Core logic supply brownout detector | Same state as in Active mode                          | Software configured    | OFF                 | OFF                            |

| AN13530     | All info                            | rmation provided in this document is subject to legal | disclaimers.           | © 2023 N            | XP B.V. All rights reser       |

### Table 2. Peripherals reduced power modes...continued

| Pt.          | eripherals                                                     | De                           | vice low-power      | modes               |                                |

|--------------|----------------------------------------------------------------|------------------------------|---------------------|---------------------|--------------------------------|

| Name         | Description                                                    | Sleep mode                   | Deep sleep<br>mode  | Power-down<br>mode  | Deep<br>Power-<br>down<br>mode |

| BODVDDMAIN   | VDD_MAIN supply<br>brownout detector                           | Same state as in Active mode | Software configured | OFF                 | OFF                            |

| FRO1M        | 1 MHz free running oscillator                                  | ON                           | Software configured | Software configured | Software configured            |

| FRO192M      | High-speed free running oscillator                             | ON                           | Software configured | OFF                 | OFF                            |

| FRO32K       | 32 kHz free running<br>oscillator                              | Same state as in Active mode | Software configured | Software configured | Software configured            |

| XTAL32K      | 32 kHz crystal oscillator                                      | Same state as in Active mode | Software configured | Software configured | Software configured            |

| XTALHF       | High frequency crystal oscillator                              | Same state as in Active mode | Software configured | OFF                 | OFF                            |

| PLL0         | Phase-locked loop<br>module 0                                  | Same state as in Active mode | Software configured | OFF                 | OFF                            |

| PLL1         | Phase-locked loop<br>module 1                                  | Same state as in Active mode | Software configured | OFF                 | OFF                            |

| USBFSPHY     | USB full speed physical interface                              | Same state as in Active mode | Software configured | OFF                 | OFF                            |

| COMP         | Analog comparator                                              | Same state as in Active mode | Software configured | Software configured | OFF                            |

| LDOEFUSEPROG | eFUSE programming low drop-out regulator                       | Same state as in Active mode | Software configured | OFF                 | OFF                            |

| LDOXTALHF    | High frequency crystal<br>oscillator<br>Low drop-out regulator | Same state as in Active mode | Software configured | OFF                 | OFF                            |

| LDOFLASHNV   | Non-volatile flash macro<br>low<br>Drop-out regulator          | ON                           | OFF                 | OFF                 | OFF                            |

| PLL0_SSCG    | PLL0 spread spectrum<br>clock<br>Generator                     | Same state as in Active mode | Software configured | OFF                 | OFF                            |

| HSCMP0       | High-speed comparator 0                                        | Same state as in Active mode | Software configured | OFF                 | OFF                            |

| HSCMP1       | High-speed comparator 1                                        | Same state as in Active mode | Software configured | OFF                 | OFF                            |

| HSCMP2       | High-speed comparator 2                                        | Same state as in Active mode | Software configured | OFF                 | OFF                            |

| OPAMP0       | Operational amplifier 0                                        | Same state as in Active mode | Software configured | OFF                 | OFF                            |

| Peripherals |                                      | Device low-power modes       |                     |                     |                                |

|-------------|--------------------------------------|------------------------------|---------------------|---------------------|--------------------------------|

| Name        | Description                          | Sleep mode                   | Deep sleep<br>mode  | Power-down<br>mode  | Deep<br>Power-<br>down<br>mode |

| OPAMP1      | Operational amplifier 1              | Same state as in Active mode | Software configured | OFF                 | OFF                            |

| OPAMP2      | Operational amplifier 2              | Same state as in Active mode | Software configured | OFF                 | OFF                            |

| VREF        | ADCs/DACs analog<br>reference module | Same state as in Active mode | Software configured | Software configured | OFF                            |

| CMPBIAS     | High-speed comparators biasing       | Same state as in Active mode | Software configured | OFF                 | OFF                            |

| HSCMP0_DAC  | HSCMP0 (internal) DAC                | Same state as in Active mode | Software configured | OFF                 | OFF                            |

| HSCMP1_DAC  | HSCMP1 (internal) DAC                | Same state as in Active mode | Software configured | OFF                 | OFF                            |

| HSCMP2_DAC  | HSCMP2 (internal) DAC                | Same state as in Active mode | Software configured | OFF                 | OFF                            |

| DAC0        | Digital-to-analog converter<br>0     | Same state as in Active mode | Software configured | OFF                 | OFF                            |

| DAC1        | Digital-to-analog converter<br>1     | Same state as in Active mode | Software configured | OFF                 | OFF                            |

| DAC2        | Digital-to-analog converter<br>2     | Same state as in Active mode | Software configured | OFF                 | OFF                            |

| STOP_DAC0   | DAC0 Stop mode                       | Same state as in Active mode | Software configured | OFF                 | OFF                            |

| STOP_DAC1   | DAC1 Stop mode                       | Same state as in Active mode | Software configured | OFF                 | OFF                            |

| STOP_DAC2   | DAC2 Stop mode                       | Same state as in Active mode | Software configured | OFF                 | OFF                            |

### Table 2. Peripherals reduced power modes...continued

### 3 Entering Low-power Modes and Waking up

Power usage is controlled by settings in the register within the SYSCON block, regulator settings controlled by the Power APIs, and the operating mode of the CPU. This application note describes how to enter and wake up from various low-power modes.

### 3.1 Power control API

The power control APIs provide the functions to configure the system for expected performance requirements. The following table lists the power APIs used in the application.

### Table 3. Power API ROM calls

| Function prototype                                                                                                                                                         | API description                                                                                                                                                                                               |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <pre>void POWER_EnterSleep(void);</pre>                                                                                                                                    | The <code>POWER_EnterSleep()</code> API puts the device in the Sleep low-power mode; only the activity of the Arm Cortex-M33 is stopped.                                                                      |

| <pre>void POWER_EnterDeepSleep(uint32_t exclude_<br/>from_pd[2], uint32_t sram_retention_ctrl,<br/>uint32_t wakeup_interrupts[4], uint32_t<br/>hardware_wake_ctrl);</pre>  | The POWER_EnterDeepSleep() API configures the Deep<br>sleep low-power mode. It controls which peripherals are<br>powered up and the SRAM instances low-power mode<br>during Deep sleep.                       |

| <pre>void POWER_EnterPowerDown(uint32_t exclude_<br/>from_pd[1], uint32_t sram_retention_ctrl,<br/>uint32_t wakeup_interrupts[2], uint32_t cpu_<br/>retention_addr);</pre> | The POWER_EnterPowerDown API configures the power<br>down low-power mode. It controls which peripherals are<br>powered up and which SRAM instances are in retention<br>state during power down.               |

| <pre>void POWER_EnterDeepPowerDown(uint32_t exclude_from_pd[1], uint32_t sram_retention_ ctrl, uint32_t wakeup_interrupts[2], uint32_ t wakeup_io_ctrl);</pre>             | The POWER_EnterDeepPowerDown API configures the<br>Deep power down low-power mode. It controls which<br>peripherals are powered up and which SRAM instances are<br>in retention state during Deep power down. |

### 3.1.1 POWER\_EnterSleep

The <code>POWER\_EnterSleep()</code> API puts the device in the Sleep low-power mode; only the activity of the Arm Cortex-M33 is stopped.

The device wakes up from the Sleep mode after:

- any interrupt enabled in the Cortex-M33 Nested Vector Interrupt Controller (NVIC) arrives at the processor

- any chip reset occurs (power-on reset, brownout detector reset, pin reset, and so on)

### Table 4. POWER\_EnterSleep

| Routine            | API description                                |

|--------------------|------------------------------------------------|

| Function Prototype | <pre>void POWER_EnterSleep(void);</pre>        |

| Input Parameter    | None                                           |

| Result             | None                                           |

| Description        | Configures and enters in Sleep low-power mode. |

### 3.1.2 POWER\_EnterDeepSleep

The POWER\_EnterDeepSleep() API configures the Deep sleep low-power mode. It allows controlling which peripherals are powered up and the SRAM instances low-power mode during Deep sleep. It defines which peripheral interrupts can be a wake-up source during Deep sleep.

The POWER\_EnterDeepSleep API switches the CPU and System Bus clock to 12 MHz. It is the responsibility of the user to reconfigure the CPU and System Bus clock after the function returns.

| Routine          | API Description                                                                                                                                                        |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                  | <pre>void POWER_EnterDeepSleep(uint32_t exclude_from_pd[2], uint32_t sram_<br/>retention_ctrl, uint32_t wakeup_interrupts[4], uint32_t hardware_wake_<br/>ctrl);</pre> |  |

| Input Parameters |                                                                                                                                                                        |  |

### Table 5. POWER\_EnterDeepSleep

| Routine                         | API Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| exclude_from_pd[2]              | Defines which analog peripherals shall not be powered down. It is a 2 x 32 bit-vector, with each bit of the vector corresponding to one module. The definition of the vector is given in <u>Table 6</u> and <u>Table 7</u> , and is aligned with the power_pd_bit_t type definition. For each bit field of the vector:<br>• 0: Module is powered down during Deep sleep.                                                                                                                                                                                                                       |

|                                 | 1: Module is running during Deep sleep.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| <pre>sram_retention_ ctrl</pre> | Defines which SRAM instances shall be put in the SRAM Deep sleep low-power mode during<br>Deep sleep. SRAM instances in the SRAM Deep sleep low-power mode do not lose their<br>content, but they cannot be involved in any DMA transfer during Deep sleep. SRAM instances<br>that are not required to be put in the SRAM Deep sleep low-power mode during Deep sleep<br>keep the state they were in before calling the API, that is:                                                                                                                                                          |

|                                 | • If the SRAM instance was in Active mode, it stays in the Active mode during Deep sleep and after wake-up from Deep sleep. Such SRAM instance can be involved in DMA transfer during Deep sleep.                                                                                                                                                                                                                                                                                                                                                                                              |

|                                 | • If the SRAM instance was in Deep sleep mode, it stays in the SRAM Deep sleep low-power mode during Deep sleep and after wake-up from Deep sleep. Such SRAM instance cannot be involved in DMA transfer during Deep sleep.                                                                                                                                                                                                                                                                                                                                                                    |

|                                 | • If the SRAM instance was in Shutdown mode, it stays in the SRAM Shutdown low-power mode during Deep sleep and after wake-up from Deep sleep. Such SRAM instance cannot be involved in DMA transfer during Deep sleep.                                                                                                                                                                                                                                                                                                                                                                        |

|                                 | The sram_retention_ctrl parameter is a 32-bit vector, with each bit of the vector corresponding to one SRAM instance. The definition of the vector is given in <u>Table 8</u> and is aligned with the power_sram_bit_t type definition. For each bit field of the vector:                                                                                                                                                                                                                                                                                                                      |

|                                 | <ul> <li>0: During Deep sleep, the SRAM instance keeps the state it had before entering Deep sleep.</li> <li>1: During Deep sleep, the SRAM instance is in the SRAM Deep sleep low-power mode (content preserved).</li> </ul>                                                                                                                                                                                                                                                                                                                                                                  |

|                                 | <b>Note:</b> When SDMA transfers are expected to occur during Deep sleep, make sure that the SRAM instances in which the SDMA descriptors and the Peripheral's data are stored are in Active mode during Deep sleep.                                                                                                                                                                                                                                                                                                                                                                           |

| wakeup_interrupts[4]            | Defines which peripheral interrupts can be a wake-up source during Deep sleep. It is a 4 x 32-bit vector, with each bit inside the vector corresponding to one interrupt source. The definition of the vector is given in <u>Table 9</u> , <u>Table 10</u> , <u>Table 11</u> , <u>Table 12</u> and is aligned with the low-power modes wake-up sources (#define WAKEUP_*) #defines definitions. For each bit field of the vector:<br>• 0: The associated peripheral cannot be a wake-up source during Deep sleep.<br>• 1: The associated peripheral can be a wake-up source during Deep sleep. |

| hardware_wake_ctrl              | Provides the possibility for all Flexcomm, High-Speed SPI, all DAC and DMIC to have DMA service during Deep sleep without waking up an entire device. The detailed mapping of the parameter is given in <u>Table 13</u> and is aligned with the definition of #define LOWPOWER_HWWAKE                                                                                                                                                                                                                                                                                                          |

| Result                          | None                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Description                     | Controls which peripherals are powered up and the SRAM instances low-power mode during Deep sleep. Defines which peripheral interrupts can be a wake-up source during Deep sleep.                                                                                                                                                                                                                                                                                                                                                                                                              |

### Table 5. POWER\_EnterDeepSleep...continued

### Table 6. Parameter exclude\_from\_pd[0] definition (1st vector)

| Bit | Symbol  | Description | Value                                                |

|-----|---------|-------------|------------------------------------------------------|

| 1:0 | -       | Reserved    | Must be set to 0                                     |

| 2   | BODCORE | - 5 11 5    | <ul><li>0: Powered down</li><li>1: Running</li></ul> |

AN13530 Application note © 2023 NXP B.V. All rights reserved.

| Bit   | Symbol       | Description                                              | Value                                                |

|-------|--------------|----------------------------------------------------------|------------------------------------------------------|

| 3     | BODVDDMAIN   | VDD_MAIN supply brown-out detector                       | <ul><li>0: Powered down</li><li>1: Running</li></ul> |

| 4     | FRO1M        | 1 MHz free running oscillator                            | <ul><li>0: Powered down</li><li>1: Running</li></ul> |

| 5     | FRO192M      | High-speed free running oscillator                       | <ul><li>0: Powered down</li><li>1: Running</li></ul> |

| 6     | FRO32K       | 32 kHz free running oscillator                           | <ul><li>0: Powered down</li><li>1: Running</li></ul> |

| 7     | XTAL32K      | 32 kHz crystal oscillator                                | <ul><li>0: Powered down</li><li>1: Running</li></ul> |

| 8     | XTALHF       | High-frequency crystal oscillator                        | <ul><li>0: Powered down</li><li>1: Running</li></ul> |

| 9     | PLL0         | Phase-locked loop module 0                               | 0: Powered down     1: Running                       |

| 10    | PLL1         | Phase-locked loop module 1                               | 0: Powered down     1: Running                       |

| 11    | USBFSPHY     | USB full speed physical interface                        | 0: Powered down     1: Running                       |

| 12    | -            | Reserved                                                 | Must be set to 0                                     |

| 13    | COMP         |                                                          | 0: Powered down     1: Running                       |

| 17:14 | -            | Reserved                                                 | Must be set to 0                                     |

| 18    | LDOEFUSEPROG | eFUSE programming low drop-out regulator                 | 0: Powered down     1: Running                       |

| 19    | -            | Reserved                                                 | Must be set to 0                                     |

| 20    | LDOXTALHF    | High-frequency crystal oscillator low drop-out regulator | <ul><li>0: Powered down</li><li>1: Running</li></ul> |

| 22:21 | -            | Reserved                                                 | Must be set to 0                                     |

| 23    | PLL0_SSCG    | PLL0 spread spectrum clock generator                     | <ul><li>0: Powered down</li><li>1: Running</li></ul> |

| 24    | -            | Reserved                                                 | Must be set to 0                                     |

| 25    | HSCMP0       | High-speed comparator 0                                  | 0: Powered down     1: Running                       |

| 26    | HSCMP1       | High-speed comparator 1                                  | 0: Powered down     1: Running                       |

| 27    | HSCMP2       | High-speed comparator 2                                  | 0: Powered down     1: Running                       |

| 28    | OPAMP0       | Operational amplifier 0                                  | 0: Powered down     1: Running                       |

| 29    | OPAMP1       | Operational amplifier 1                                  | <ul><li>0: Powered down</li><li>1: Running</li></ul> |

Table 6. Parameter exclude\_from\_pd[0] definition (1st vector)...continued

AN13530 Application note

| Bit | Symbol | Description                       | Value                                                |

|-----|--------|-----------------------------------|------------------------------------------------------|

| 30  | OPAMP2 | Operational amplifier 2           | <ul><li>0: Powered down</li><li>1: Running</li></ul> |

| 31  | VREF   | ADCs/DACs analog reference module | <ul><li>0: Powered down</li><li>1: Running</li></ul> |

### Table 6. Parameter exclude\_from\_pd[0] definition (1st vector)...continued

### Table 7. Parameter exclude\_from\_pd[1] definition (2nd vector)

| Bit   | Symbol     | Description                    | Value                                                                |

|-------|------------|--------------------------------|----------------------------------------------------------------------|

| 0     | CMPBIAS    | High-speed comparators biasing | O: Powered down     1: Running                                       |

| 1     | HSCMP0_DAC | HSCMP0 (internal) DAC          | <ul><li>0: Powered down</li><li>1: Running</li></ul>                 |

| 2     | HSCMP1_DAC | HSCMP1 (internal) DAC          | <ul><li>0: Powered down</li><li>1: Running</li></ul>                 |

| 3     | HSCMP2_DAC | HSCMP2 (internal) DAC          | 0: Powered down     1: Running                                       |

| 4     | DAC0       | Digital-to-analog converter 0  | <ul><li>0: Powered down</li><li>1: Running</li></ul>                 |

| 5     | DAC1       | Digital-to-analog converter 1  | <ul><li>0: Powered down</li><li>1: Running</li></ul>                 |

| 6     | DAC2       | Digital-to-analog converter 2  | 0: Powered down     1: Running                                       |

| 7     | STOP_DAC0  | DAC0 Stop mode                 | <ul><li>0: Stop mode enabled</li><li>1: Stop mode disabled</li></ul> |

| 8     | STOP_DAC1  | DAC1 Stop mode                 | <ul><li>0: Stop mode enabled</li><li>1: Stop mode disabled</li></ul> |

| 9     | STOP_DAC2  | DAC2 Stop mode                 | <ul><li>0: Stop mode enabled</li><li>1: Stop mode disabled</li></ul> |

| 31:10 | -          | Reserved                       | Must be set to 0                                                     |

### Table 8. Parameter sram\_retention\_ctrl

| Bit | SRAM instance (SRAM size) | Value                                                                                                   |

|-----|---------------------------|---------------------------------------------------------------------------------------------------------|

| 0   | RAM_X0 (16 kB)            | <ul><li>0: Keeps state prior entering Deep sleep</li><li>1: Deep sleep (content preserved)</li></ul>    |

| 1   | RAM_00 (4 kB)             | <ul><li>0: Keeps state prior entering Deep sleep</li><li>1: Deep sleep (content preserved)</li></ul>    |

| 2   | RAM_01 (4 kB)             | <ul><li>0: Keeps state prior entering Deep sleep</li><li>1: Deep sleep (content preserved)</li></ul>    |

| 3   | RAM_02 (4 kB)             | <ul><li>0: Keeps state prior entering Deep sleep</li><li>1: Deep sleep (content preserved)</li></ul>    |

| 4   | RAM_03 (4 kB)             | <ul> <li>0: Keeps state prior entering Deep sleep</li> <li>1: Deep sleep (content preserved)</li> </ul> |

AN13530

10 / 39

| Bit   | SRAM instance (SRAM size) | Value                                                                                                |

|-------|---------------------------|------------------------------------------------------------------------------------------------------|

| 5     | RAM_10 (16 kB)            | <ul><li>0: Keeps state prior entering Deep sleep</li><li>1: Deep sleep (content preserved)</li></ul> |

| 6     | RAM_20 (32 kB)            | <ul><li>0: Keeps state prior entering Deep sleep</li><li>1: Deep sleep (content preserved)</li></ul> |

| 7     | RAM_30 (32 kB)            | <ul><li>0: Keeps state prior entering Deep sleep</li><li>1: Deep sleep (content preserved)</li></ul> |

| 8     | RAM_40 (4 kB)             | <ul><li>0: Keeps state prior entering Deep sleep</li><li>1: Deep sleep (content preserved)</li></ul> |

| 9     | RAM_41 (4 kB)             | <ul><li>0: Keeps state prior entering Deep sleep</li><li>1: Deep sleep (content preserved)</li></ul> |

| 10    | RAM_42 (4 kB)             | <ul><li>0: Keeps state prior entering Deep sleep</li><li>1: Deep sleep (content preserved)</li></ul> |

| 11    | RAM_43 (4 kB)             | <ul><li>0: Keeps state prior entering Deep sleep</li><li>1: Deep sleep (content preserved)</li></ul> |

| 31:12 | Reserved                  | Must be set to 0                                                                                     |

### Table 8. Parameter sram\_retention\_ctrl...continued

### Table 9. Parameter wakeup\_interrupts[0] (1st vector)

| Bit | Symbol      | Description                                             | Value                                                                  |

|-----|-------------|---------------------------------------------------------|------------------------------------------------------------------------|

| 0   | SYS         | Watchdog, brownout Detectors (BOD VDDMAIN and BOD Core) | <ul><li>0: Interrupt disabled</li><li>1: Interrupt enabled</li></ul>   |

| 1   | SDMA0       | SDMA0 controller                                        | <ul><li>0: Interrupt disabled</li><li>1: Interrupt enabled</li></ul>   |

| 2   | GLOBALINT0  | Group GPIO input interrupt 0 (GINT0)                    | <ul><li>0: Interrupt disabled</li><li>1: Interrupt enabled</li></ul>   |

| 3   | GLOBALINT1  | Group GPIO input interrupt 1 (GINT1)                    | <ul><li>0: Interrupt disabled</li><li>1: Interrupt enabled</li></ul>   |

| 4   | GPIO_INT0_0 | Pin interrupt 0 or pattern match engine slice 0 (PINT0) | <ul><li>0: Interrupt disabled</li><li>1: Interrupt enabled</li></ul>   |

| 5   | GPIO_INT0_1 | Pin interrupt 1 or pattern match engine slice 1 (PINT1) | <ul><li>0: Interrupt disabled</li><li>1: Interrupt enabled</li></ul>   |

| 6   | GPIO_INT0_2 | Pin interrupt 2 or pattern match engine slice 2 (PINT2) | <ul><li>0: Interrupt disabled</li><li>1: Interrupt enabled</li></ul>   |

| 7   | GPIO_INT0_3 | Pin interrupt 3 or pattern match engine slice 3 (PINT3) | <ul><li>0: Interrupt disabled</li><li>1: Interrupt enabled</li></ul>   |

| 8   | UTICK       | Micro-tick timer                                        | <ul><li>0: Interrupt disabled</li><li>1: Interrupt enabled</li></ul>   |

| 9   | -           | Reserved                                                | Must be set to 0                                                       |

| 10  | CTIMER0     | Standard counter/timer<br>CTIMER0                       | <ul><li> 0: Interrupt disabled</li><li> 1: Interrupt enabled</li></ul> |

| 11  | CTIMER1     | Standard counter/timer<br>CTIMER1                       | <ul><li> 0: Interrupt disabled</li><li> 1: Interrupt enabled</li></ul> |

| Bit   | Symbol       | Description                                      | Value                                                                  |

|-------|--------------|--------------------------------------------------|------------------------------------------------------------------------|

| 12    | -            | Reserved                                         | Must be set to 0                                                       |

| 13    | CTIMER3      | Standard counter/timer<br>CTIMER3                | <ul><li> 0: Interrupt disabled</li><li> 1: Interrupt enabled</li></ul> |

| 14    | FLEXCOMM0    | Flexcomm Interface 0<br>(USART, SPI, I2C)        | <ul><li> 0: Interrupt disabled</li><li> 1: Interrupt enabled</li></ul> |

| 15    | FLEXCOMM1    | Flexcomm Interface 1<br>(USART, SPI, I2C)        | <ul><li> 0: Interrupt disabled</li><li> 1: Interrupt enabled</li></ul> |

| 16    | FLEXCOMM2    | Flexcomm Interface 2<br>(USART, SPI, I2C)        | <ul><li> 0: Interrupt disabled</li><li> 1: Interrupt enabled</li></ul> |

| 17    | FLEXCOMM3    | Flexcomm Interface 3<br>(USART, SPI, I2C)        | <ul><li> 0: Interrupt disabled</li><li> 1: Interrupt enabled</li></ul> |

| 18    | FLEXCOMM4    | Flexcomm Interface 4<br>(USART, SPI, I2C)        | <ul><li> 0: Interrupt disabled</li><li> 1: Interrupt enabled</li></ul> |

| 19    | FLEXCOMM5    | Flexcomm Interface 5<br>(USART, SPI, I2C)        | <ul><li> 0: Interrupt disabled</li><li> 1: Interrupt enabled</li></ul> |

| 20    | FLEXCOMM6    | Flexcomm Interface 6<br>(USART, SPI, I2C)        | <ul><li> 0: Interrupt disabled</li><li> 1: Interrupt enabled</li></ul> |

| 21    | FLEXCOMM7    | Flexcomm Interface 7<br>(USART, SPI, I2C)        | <ul><li> 0: Interrupt disabled</li><li> 1: Interrupt enabled</li></ul> |

| 23:22 | -            | Reserved                                         | Must be set to 0                                                       |

| 24    | ACMP         | Analog comparator                                | <ul><li> 0: Interrupt disabled</li><li> 1: Interrupt enabled</li></ul> |

| 25    | -            | Reserved                                         | Must be set to 0                                                       |

| 26    | HWVAD        | Hardware voice activity detector                 | <ul><li> 0: Interrupt disabled</li><li> 1: Interrupt enabled</li></ul> |

| 27    | USB0_NEEDCLK | USB full speed                                   | <ul><li> 0: Interrupt disabled</li><li> 1: Interrupt enabled</li></ul> |

| 28    | -            | Reserved                                         | Must be set to 0                                                       |

| 29    | RTC          | Real-time clock (counter event and tamper event) | <ul><li> 0: Interrupt disabled</li><li> 1: Interrupt enabled</li></ul> |

| 31:30 | -            | Reserved                                         | Must be set to 0                                                       |

|       | 1            | 1                                                | 1                                                                      |

Table 9. Parameter wakeup\_interrupts[0] (1st vector)...continued

### Table 10. Parameter wakeup\_interrupts[1] (2nd vector)

| Bit | Symbol      | Description                                             | Value                                                                |

|-----|-------------|---------------------------------------------------------|----------------------------------------------------------------------|

| 0   | GPIO_INT0_4 | Pin interrupt 4 or pattern match engine slice 4 (PINT4) | <ul><li>0: Interrupt disabled</li><li>1: Interrupt enabled</li></ul> |

| 1   | GPIO_INT0_5 | Pin interrupt 5 or pattern match engine slice 5 (PINT5) | <ul><li>0: Interrupt disabled</li><li>1: Interrupt enabled</li></ul> |

| 2   | GPIO_INT0_6 | Pin interrupt 6 or pattern match engine slice 6 (PINT6) | <ul><li>0: Interrupt disabled</li><li>1: Interrupt enabled</li></ul> |

| Bit   | Symbol          | Description                                                                 | Value                                                                  |

|-------|-----------------|-----------------------------------------------------------------------------|------------------------------------------------------------------------|

| 3     | GPIO_INT0_7     | Pin interrupt 7 or pattern match engine slice 7 (PINT7)                     | <ul><li> 0: Interrupt disabled</li><li> 1: Interrupt enabled</li></ul> |

| 4     | CTIMER2         | Standard counter/timer CTIMER2                                              | <ul><li> 0: Interrupt disabled</li><li> 1: Interrupt enabled</li></ul> |

| 5     | CTIMER4         | Standard counter/timer CTIMER4                                              | <ul><li>0: Interrupt disabled</li><li>1: Interrupt enabled</li></ul>   |

| 6     | OS_EVENT_TIMER  | OS Event Timer                                                              | <ul><li>0: Interrupt disabled</li><li>1: Interrupt enabled</li></ul>   |

| 12:7  | -               | Reserved                                                                    | Must be set to 0                                                       |

| 13    | SPIFILTER       | SPI Filter                                                                  | <ul><li> 0: Interrupt disabled</li><li> 1: Interrupt enabled</li></ul> |

| 17:14 | -               | Reserved                                                                    | Must be set to 0                                                       |

| 18    | SEC_GPIO_INT0_0 | Secure Pin interrupt 0 or pattern match engine<br>slice 0<br>(Secure PINT0) | <ul><li>0: Interrupt disabled</li><li>1: Interrupt enabled</li></ul>   |

| 19    | SEC_GPIO_INT0_1 | Secure Pin interrupt 1 or pattern match engine<br>slice 1<br>(Secure PINT1) | <ul><li>0: Interrupt disabled</li><li>1: Interrupt enabled</li></ul>   |

| 25:20 | -               | Reserved                                                                    | Must be set to 0                                                       |

| 26    | SDMA1           | SDMA1 control                                                               | <ul><li>0: Interrupt disabled</li><li>1: Interrupt enabled</li></ul>   |

| 27    | LSPI_HS         | High-Speed SPI                                                              | <ul><li>0: Interrupt disabled</li><li>1: Interrupt enabled</li></ul>   |

| 29:28 | -               | Reserved                                                                    | Must be set to 0                                                       |

| 30    | 13C             | МІРІ ІЗС                                                                    | <ul><li> 0: Interrupt disabled</li><li> 1: Interrupt enabled</li></ul> |

| 31    | -               | Reserved                                                                    | Must be set to 0                                                       |

Table 10. Parameter wakeup\_interrupts[1] (2nd vector)...continued

Table 11. Parameter wakeup\_interrupts[2] (3rd vector)

| Bit   | Symbol | Description                   | Value                                                                  |

|-------|--------|-------------------------------|------------------------------------------------------------------------|

| 1:0   | -      | Reserved                      | Must be set to 0                                                       |

| 2     | -      | Reserved                      | Must be set to 0                                                       |

| 9:3   | -      | Reserved                      | Must be set to 0                                                       |

| 10    | DAC0   | Digital-to-analog converter 0 | <ul><li> 0: Interrupt disabled</li><li> 1: Interrupt enabled</li></ul> |

| 11    | DAC1   | Digital-to-analog converter 1 | <ul><li> 0: Interrupt disabled</li><li> 1: Interrupt enabled</li></ul> |

| 12    | DAC2   | Digital-to-analog converter 2 | <ul><li> 0: Interrupt disabled</li><li> 1: Interrupt enabled</li></ul> |

| 31:13 | -      | Reserved                      | Must be set to 0                                                       |

AN13530 Application note © 2023 NXP B.V. All rights reserved.

## Bit Symbol Description Value 31:0 Reserved Must be set to 0

### Table 13. Parameter hardware\_wake\_ctrl

| Bit  | Symbol                 | Description                                                                                                                                                                                                                                                                                                                                | Value                                            |

|------|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|

| 0    | -                      | Reserved                                                                                                                                                                                                                                                                                                                                   | Must be set to 0                                 |

| 1    | HWWAKE_<br>PERIPHERALS | Wake for Flexcomms. Any Flexcomm FIFO reaching the level specified by its own TXLVL causes peripheral clocking to wake up temporarily while the related status is asserted                                                                                                                                                                 | <ul><li>0: Disabled</li><li>1: Enabled</li></ul> |

| 2    | HWWAKE_DMIC            | Wake for Digital Microphone (DMIC). When 1, the DMIC input FIFO reaching the level specified by TRIGLVL of either channel causes peripheral clocking to be enabled temporarily while the DMIC FIFO level is at or above TRIGLVL. This allows DMA to become active to move data out of the DMIC FIFO. Used with LOWPOWER_HWWAKE_PERIPHERALS | <ul><li>0: Disabled</li><li>1: Enabled</li></ul> |

| 3    | HWWAKE_SDMA0           | Wake for SDMA0. SDMA0 being busy causes peripheral clocking to remain running until DMA completes. Used with HWWAKE_PERIPHERALS                                                                                                                                                                                                            | <ul><li>0: Disabled</li><li>1: Enabled</li></ul> |

| 4    | -                      | Reserved                                                                                                                                                                                                                                                                                                                                   | Must be set to 0                                 |

| 5    | HWWAKE_SDMA1           | Wake for SDMA1. SDMA1 being busy causes peripheral clocking to remain running until DMA completes. Used with HWWAKE_PERIPHERALS                                                                                                                                                                                                            | <ul><li>0: Disabled</li><li>1: Enabled</li></ul> |

| 6    | HWWAKE_DAC             | Wake for DAC0, DAC1, DAC2. Any DAC0/1/2 FIFO reaching the level specified by the configuration generates an asynchronous SDMA0 request, and SDMA0 wakes up the bus clock temporarily to transfer data to DAC0/1/2                                                                                                                          | <ul><li>0: Disabled</li><li>1: Enabled</li></ul> |

| 31:7 | -                      | Reserved                                                                                                                                                                                                                                                                                                                                   | Must be set to 0                                 |

### 3.1.3 POWER\_EnterPowerDown

The POWER\_EnterPowerDown API configures the power down low-power mode and allows controlling which peripherals are powered up and which SRAM instances are in retention state during power down.

When a wake-up event occurs, CPU resumes code execution after the call to the low-power API function. However, during power down, a couple of modules lose their states and therefore, they must be reconfigured by the user application.

It is the responsibility of the user to make sure that the SRAM instance(s) containing the application software stacks and variables are preserved during power down.

The POWER\_EnterPowerDown API switches the CPU and System Bus clock to 12 MHz. It is the responsibility of the user to reconfigure the CPU and System Bus clock after the function returns.

During power down, a couple of modules lose their state. It is the responsibility of the user application to reconfigure them if the application requires them.

### Table 14. POWER\_EnterPowerDown

| Routine              | API Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Function Prototype   | <pre>void POWER_EnterPowerDown(uint32_t exclude_from_pd[1], uint32_t sram_<br/>retention_ctrl, uint32_t wakeup_interrupts[2], uint32_t cpu_retention_<br/>addr);</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                      | Input Parameters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| exclude_from_pd[1]   | <ul> <li>Defines which analog peripherals shall not be powered down. It is a 1 x 32-bit vector, with each bit of the vector corresponding to one module. The definition of the vector is given in <u>Table 15</u>, and is aligned with the power_pd_bit_t type definition. For each bit field of the vector:</li> <li>0: The module is powered down during power down.</li> <li>1: The module is running during power down.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| sram_retention_ctrl  | <ul> <li>Defines which SRAM instances shall preserve their content during power down. The sram_retention_ctrl parameter is a 32-bit vector, with each bit of the vector corresponding to one SRAM instance. The definition of the vector is given in Table 16, and is aligned with the power_sram_bit_t type definition. For each bit field of the vector:</li> <li>0: During power down, the SRAM instance is in the SRAM Shut-down low-power mode (content not preserved).</li> <li>1: During power down, the SRAM instance is in the SRAM Deep sleep low-power mode (content preserved).</li> <li>Note: The SRAM instance, which is used to save Cortex-M33, AHB secure controller and Flash PRINCE modules states, is automatically put in the Deep sleep low-power mode (content</li> </ul>                                                                                                                                                                                    |

| wakeup_interrupts[2] | <ul> <li>preserved) by Low power.</li> <li>Defines which peripheral interrupts can be a wake-up source during power down. It is a 2 x 32-bit vector, with each bit inside the vector corresponding to one interrupt source. The definition of the vector is given in <u>Table 17</u> and <u>Table 18</u>, and is aligned with the Low-power modes wake-up sources (#define WAKEUP_*) #defines definitions. For each bit field of the vector:</li> <li>0: The associated peripheral cannot be a wake-up source during power down</li> <li>1: The associated peripheral can be a wake-up source during power down</li> </ul>                                                                                                                                                                                                                                                                                                                                                          |

|                      | <b>Note:</b> In case Flexcomm3 UART is used as wake-up source, a 32 kHz clock source (either FRO32K or XTAL32K) must be enabled during power down. The unique baud rate supported is 9600 Baud.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| cpu_retention_addr   | <ul> <li>Defines the start address of the area inside SRAM region where the Cortex-M33, AHB secure controller, and Flash PRINCE modules state are saved during power down:</li> <li>Must be word-aligned (address ending by 0x0, 0x4, 0x8, and 0xC)</li> <li>Can be any value: <ul> <li>Between 0x20000000 and 0x200009FC (inside RAM_00)</li> <li>Between 0x20001000 and 0x200019FC (inside RAM_01)</li> <li>Between 0x20002000 and 0x200029FC (inside RAM_02)</li> <li>Between 0x20003000 and 0x200039FC (inside RAM_03)</li> </ul> </li> <li>If the parameter does not meet the boundaries mentioned above, it is set to 0x20000000 (start of RAM_00) by the low-power API.</li> <li>Note: The states of the Cortex-M33, AHB security controller, and PRINCE modules are stored in SRAM from cpu_retention_addr to cpu_retention_addr + 1540 Bytes - 1. Therefore, any user data present in this area before calling the function is overwritten and definitely lost.</li> </ul> |

| Result               | None                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Description          | Controls which peripherals are powered up and which SRAM instances are in retention state during power down. Defines which SRAM instances shall preserve their content during power down.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Bit   | Symbol  | Description                       | Value                          |

|-------|---------|-----------------------------------|--------------------------------|

| 3:0   | -       | Reserved                          | Must be set to 0               |

| 4     | FRO1M   | 1 MHz free running oscillator     | O: Powered down     1: Running |

| 5     | -       | Reserved                          | Must be set to 0               |

| 6     | FRO32K  | 32 kHz free running oscillator    | O: Powered down     1: Running |

| 7     | XTAL32K | 32 kHz crystal oscillator         | O: Powered down     1: Running |

| 12:8  | -       | Reserved                          | Must be set to 0               |

| 13    | COMP    | Analog comparator                 | O: Powered down     1: Running |

| 30:14 | -       | Reserved                          | Must be set to 0               |

| 31    | VREF    | ADCs/DACs analog reference module | O: Powered down     1: Running |

### Table 15. Parameter exclude\_from\_pd[0] definition

### Table 16. Parameter sram\_retention\_ctrl

| Bit | SRAM instance (SRAM size) | Value                                                                                            |

|-----|---------------------------|--------------------------------------------------------------------------------------------------|

| 0   | RAM_X0 (16 kB)            | <ul><li>0: Shut Down (content not preserved)</li><li>1: Deep Sleep (content preserved)</li></ul> |

| 1   | RAM_00 (4 kB)             | <ul><li>0: Shut Down (content not preserved)</li><li>1: Deep Sleep (content preserved)</li></ul> |

| 2   | RAM_01 (4 kB)             | <ul><li>0: Shut Down (content not preserved)</li><li>1: Deep Sleep (content preserved)</li></ul> |

| 3   | RAM_02 (4 kB)             | <ul><li>0: Shut Down (content not preserved)</li><li>1: Deep Sleep (content preserved)</li></ul> |

| 4   | RAM_03 (4 kB)             | <ul><li>0: Shut Down (content not preserved)</li><li>1: Deep Sleep (content preserved)</li></ul> |

| 5   | RAM_10 (16 kB)            | <ul><li>0: Shut Down (content not preserved)</li><li>1: Deep Sleep (content preserved)</li></ul> |

| 6   | RAM_20 (32 kB)            | <ul><li>0: Shut Down (content not preserved)</li><li>1: Deep Sleep (content preserved)</li></ul> |

| 7   | RAM_30 (32 kB)            | <ul><li>0: Shut Down (content not preserved)</li><li>1: Deep Sleep (content preserved)</li></ul> |

| 8   | RAM_40 (4 kB)             | <ul><li>0: Shut Down (content not preserved)</li><li>1: Deep Sleep (content preserved)</li></ul> |

| 9   | RAM_41 (4 kB)             | <ul><li>0: Shut Down (content not preserved)</li><li>1: Deep Sleep (content preserved)</li></ul> |

| 10  | RAM_42 (4 kB)             | <ul><li>0: Shut Down (content not preserved)</li><li>1: Deep Sleep (content preserved)</li></ul> |

| 11  | RAM_43 (4 kB)             | <ul><li>0: Shut Down (content not preserved)</li><li>1: Deep Sleep (content preserved)</li></ul> |

© 2023 NXP B.V. All rights reserved.

|       | SRAM instance (SRAM size) |                  |

|-------|---------------------------|------------------|

| 31:12 | Reserved                  | Must be set to 0 |

### Table 40 Devenue for eveny vetention styl

### Table 17. Parameter wakeup\_interrupts[0] (1st vector)

| Bit   | Symbol     | Description                                      | Value                                                                  |

|-------|------------|--------------------------------------------------|------------------------------------------------------------------------|

| 1:0   | -          | Reserved                                         | Must be set to 0                                                       |

| 2     | GLOBALINT0 | Group GPIO input interrupt 0 (GINT0)             | <ul><li> 0: Interrupt disabled</li><li> 1: Interrupt enabled</li></ul> |

| 3     | GLOBALINT1 | Group GPIO input interrupt 1 (GINT1)             | <ul><li> 0: Interrupt disabled</li><li> 1: Interrupt enabled</li></ul> |

| 16:4  | -          | Reserved                                         | Must be set to 0                                                       |

| 17    | FLEXCOMM3  | Any module inside Flexcomm3 (UART, SPI, I2C)     | <ul><li> 0: Interrupt disabled</li><li> 1: Interrupt enabled</li></ul> |

| 23:18 | -          | Reserved                                         | Must be set to 0                                                       |

| 24    | ACMP       | Analog comparator                                | <ul><li> 0: Interrupt disabled</li><li> 1: Interrupt enabled</li></ul> |

| 28:25 | -          | Reserved                                         | Must be set to 0                                                       |

| 29    | RTC        | Real-time clock (counter event and tamper event) | <ul><li> 0: Interrupt disabled</li><li> 1: Interrupt enabled</li></ul> |

| 31:30 | -          | Reserved                                         | Must be set to 0                                                       |

### Table 18. Parameter wakeup\_interrupts[1] (2nd vector)

| Bit  | Symbol  | Description | Value                                                                |

|------|---------|-------------|----------------------------------------------------------------------|

| 5:0  | -       | Reserved    | Must be set to 0                                                     |

| 6    | OSTIMER |             | <ul><li>0: Interrupt disabled</li><li>1: Interrupt enabled</li></ul> |

| 31:7 | -       | Reserved    | Must be set to 0                                                     |

### 3.1.4 POWER\_EnterDeepPowerDown

The POWER EnterDeepPowerDown API configures the Deep power-down low-power mode. It allows controlling which peripherals are powered up and which SRAM instances are in retention state during the Deep power-down.

The POWER EnterDeepPowerDown API switches the CPU and System Bus clock to 12 MHz. It is the responsibility of the user to reconfigure the CPU and System Bus clock after the function has returned (this happens when the Deep power-down state is not entered because an RTC or OS Event Timer interrupt is pending when the API is called. Otherwise, this API never returns).

| Routine            | API Description                                                                                                                                                |  |

|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Function Prototype | <pre>void POWER_EnterDeepPowerDown (uint32_t exclude_from_pd[1], uint32_t sram_retention_ctrl, uint32_t wakeup_interrupts[2], uint32_t wakeup_ io_ctrl);</pre> |  |

Table 19. POWER\_EnterDeepPowerDown

| Routine              | API Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

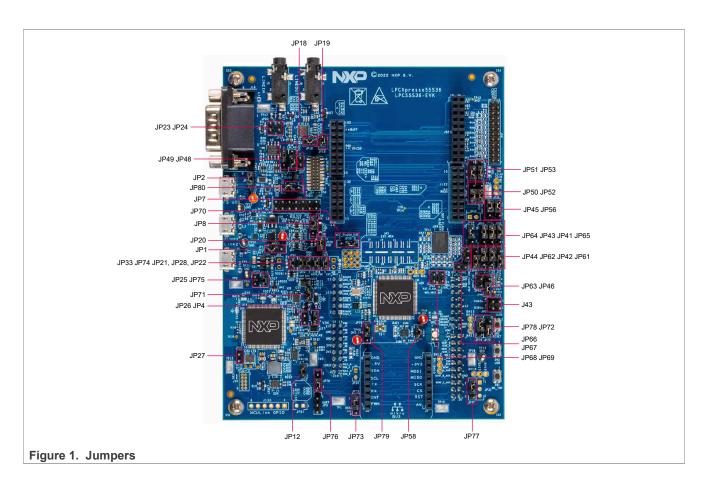

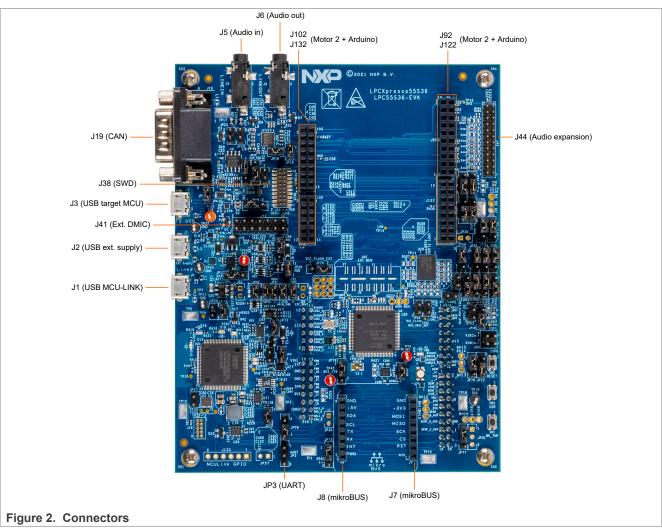

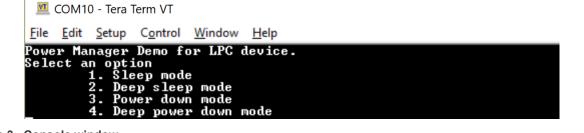

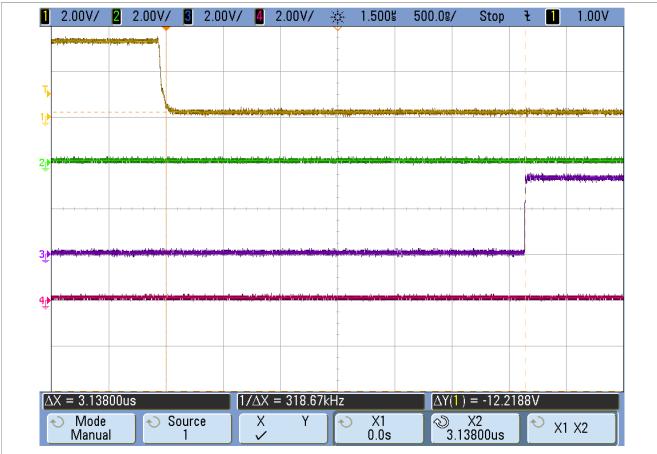

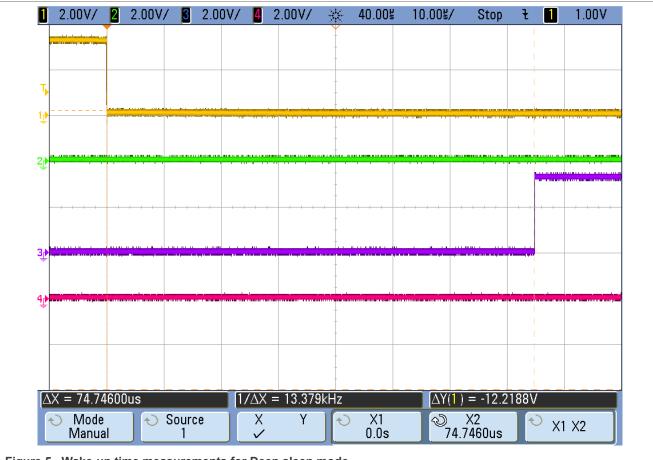

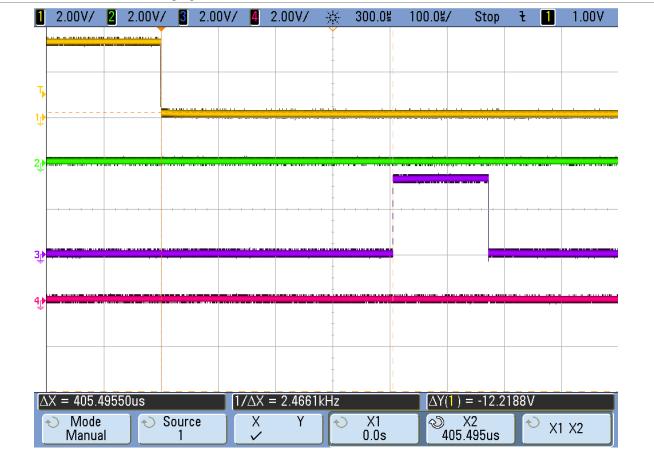

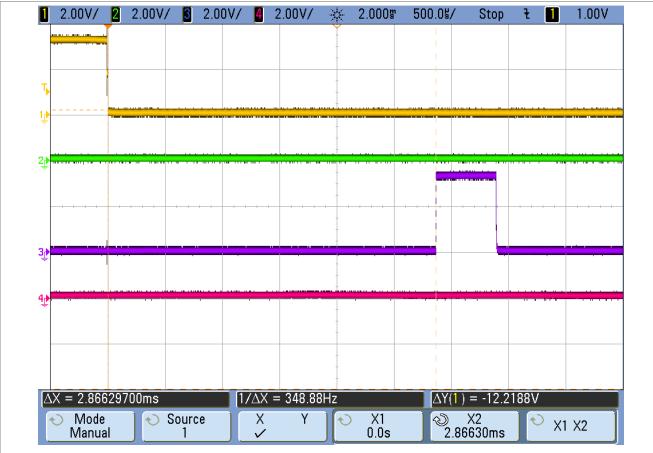

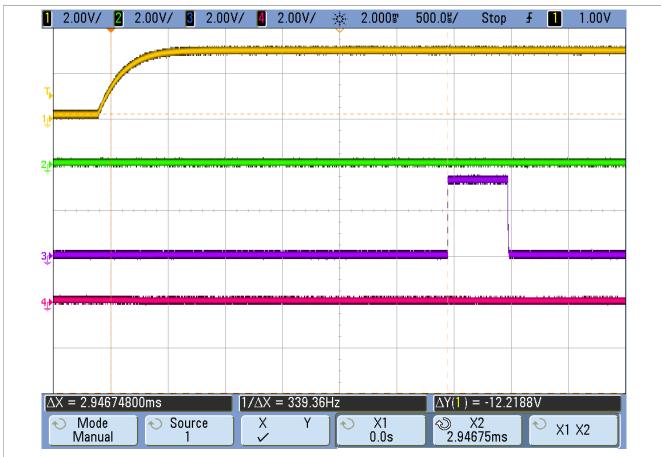

|                      | Input Parameters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |